Address translation unit (pci express)—intel, Bit default description – Intel CONTROLLERS 413808 User Manual

Page 343

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

343

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

3.17.58 PCI Express Device Capabilities Register - PCIE_DCAP

This register identifies the capabilities and current operating mode of ATU, DMAs and

Message Unit when operating in the PCI Express mode.

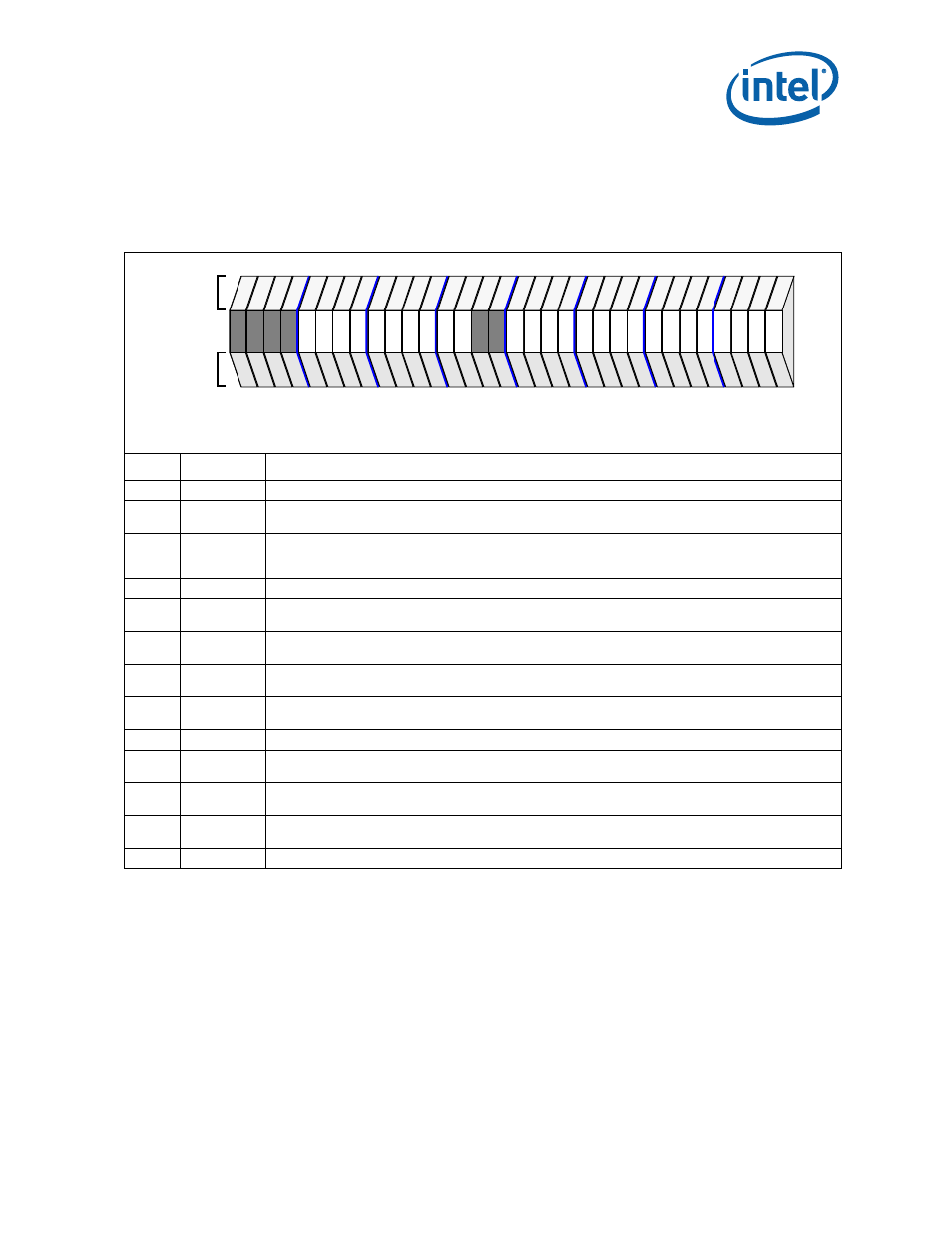

Table 198. PCI Express Device Capabilities Register - PCIE_DCAP

Bit

Default

Description

31:28

00

2

Preserved

27:26

00

Captured Slot Power Limit Scale - Specifies the scale used for the Slot Power Limit Value. This value is

set when the Set_Slot_Power_Limit message is received.

25:18

00H

Captured Slot Power Limit Value - In combination with the Slot Power Limit Scale value, specifies the

upper limit on power supplied by slot. This value is set when the Set_Slot_Power_Limit message is

received.

17:16

00

Preserved

15

1

Role-Based Error Reporting - this bit is set to indicate that this device implements the Role Base Error

Reporting defined in PCI Express Base Specification, Revision 1.1.

14

0

Power Indicator Present on Device - When set, indicates that a Power Indicator is implemented on the

card or module.

13

0

Attention Indicator Preset on Device - When set, indicates that an Attention Indicator is implemented on

the card or module

12

0

Attention Button Present on Device - When set, indicates that an Attention Button is implemented on

the card or module

11:9

000

Endpoint L1 Acceptable Latency - 4138xx does not support L1 active state power management.

8:6

111

Endpoint L0 Acceptable Latency -Total acceptable latency that 4138xx can withstand due to a transition

from L0s to L0 state.

5

0

Extended Tag Field Supported - Indicates the maximum supported size of the Tag field as a Requester.

4138xx does not generate 8-bit Tags but supports 8-bit Tags as a completer.

4:3

00

Phantom Functions Supported

The ATU does not use phantom functions to extend the number of outstanding requests.

2:0

010

Max Payload Size Supported - Indicates that 4138xx can support a max payload of 512B

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

pr

pr

pr

pr

pr

pr

pr

pr

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

pr

pr

pr

pr

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+0D4H