Intel CONTROLLERS 413808 User Manual

Page 140

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

140

Order Number: 317805-001US

In the ATU Status Register (

) the appropriate bit is set indicating that the

Extended Capability Configuration space is supported. When this bit is read, the device

can then read the Capabilities Pointer register (

) to determine the

configuration offset of the Extended Capabilities Configuration Header. The format of

these headers are depicted in

,

and

.

.

The first byte at the Extended Configuration Offset 98H is the ATU Capability Identifier

Register (

Section

). This identifies this Extended Configuration Header space as the

type defined by the PCI Bus Power Management Interface Specification, Revision 1.1.

Following the Capability Identifier Register is the single byte Next Item Pointer Register

) which indicates the configuration offset of an additional Extended

Capabilities Header, when supported. In the ATU, the Next Item Pointer Register is set

to B0H indicating that there is an additional Extended Capabilities Headers supported in

the ATUs configuration space.

To enable the PCI Bus Power Management Interface Specification, Revision 1.1

compliance support, the Power State Transition interrupt mask in bit 8 of the ATUIMR

needs to be cleared. It is the configuration software’s responsibility to properly enable

and initialize the ATUs Power Management Interface before the Configuration Cycle

Retry Bit in the

Section 2.14.41, “PCI Configuration and Status Register - PCSR” on

is cleared in order for the ATU to be Advanced Configuration and Power

Interface Specification, Revision 2.0 compliant.

Note:

MSI-X Capability Registers are defined in

Chapter 4.0, “Messaging Unit.”

The first byte at the Extended Configuration Offset B0H is the MSI-X Capability

Identifier Register (

Section 4.7.26, “MSI-X Capability Identifier Register -

). This identifies this Extended Configuration Header space as the type

defined by the PCI Local Bus Specification, Revision 2.3.

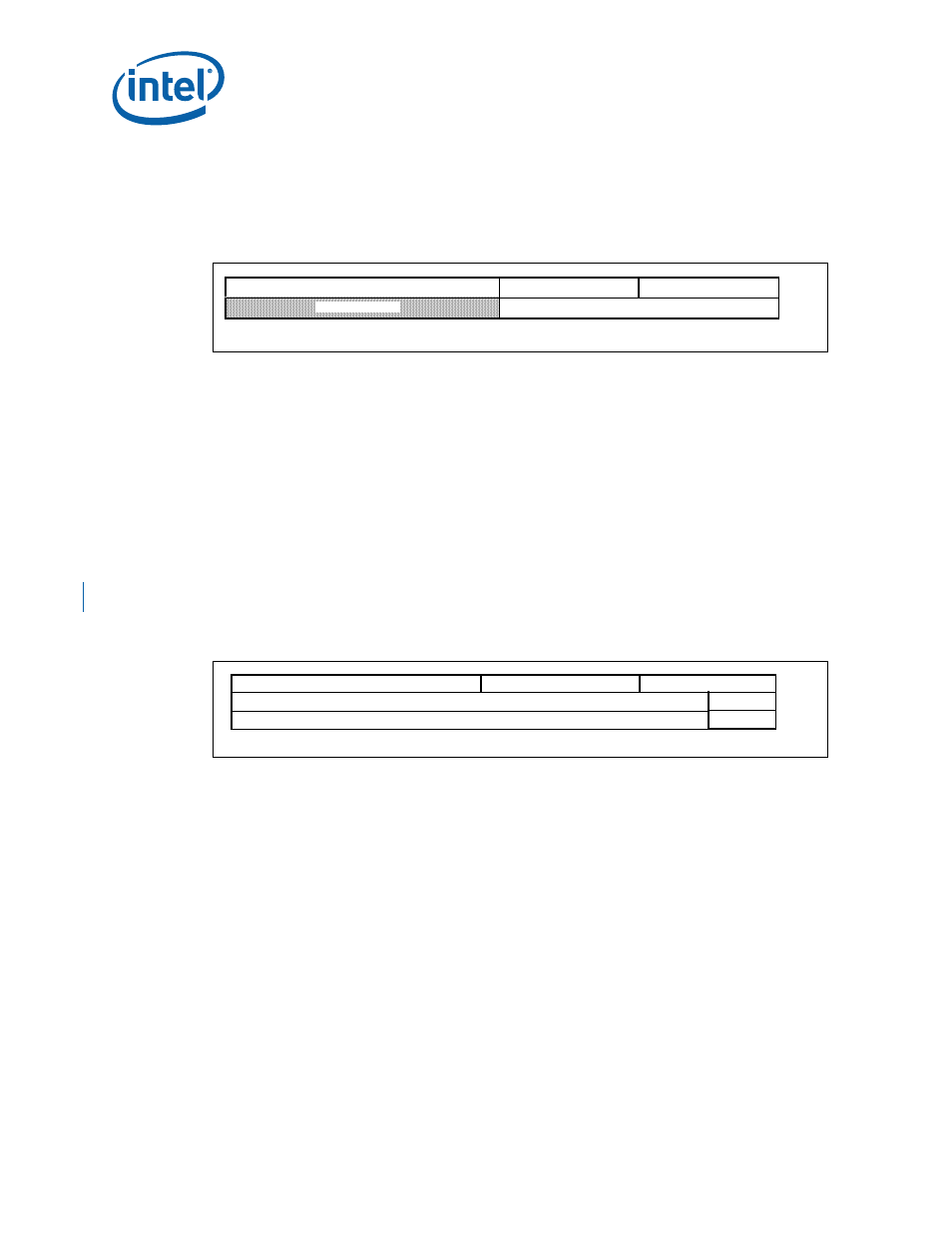

Figure 16. ATU Interface Extended Configuration Header Format (Power Management)

98H

9CH

Capability Identifier

Next Item Pointer

Power Management Capabilities

Power Management Control/Status

Reserved

B6326-01

Figure 17. ATU Interface Extended Configuration Header Format (MSI-X Capability)

B0H

B4H

MSI-X Capability ID

MSI-X Next Item Pointer

MSI-X Message Control

MSI-X Table Offset

MSI-X PBA Offset

B8H

Table BIR

PBA BIR

B6327-01