Arbiter and a, Bit default description – Intel CONTROLLERS 413808 User Manual

Page 499

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

499

System Controller (SC) and Internal Bus Bridge—Intel

®

413808 and 413812

7.5.1

Internal Bus Arbitration Control Register — IBACR

The 4138xx has two internal buses: the north internal bus and the south internal bus.

Refer to the block diagram shown in

Figure 2, “Intel® 413808 and 413812 I/O

Controllers in TPER Mode Functional Block Diagram” on page 43

. The two internal

buses are identical and provide de-multiplexed address and data buses. Therefore,

each internal bus consists of two independent arbiters: an

address

arbiter and a

data

arbiter. The north internal bus address arbiter controls the north internal bus

address

initiators, whereas the north internal data arbiter controls the north internal bus

data

initiators. Similarly, the south internal bus address arbiter controls the south internal

bus

address

initiators, whereas the south internal data arbiter controls the south

internal bus

data

initiators.

The IBACR can be used to enable or disable an internal bus

address

initiator from

acquiring the internal address bus. Note that this register does not disable the agent. It

only prevents an address initiator arbitrating for the internal address bus from

acquiring the internal address bus. Bits [15:0] control the address initiators on the

north internal address bus, and bits [31:16] control the address initiators on the south

internal address bus.

Warning:

Since the internal address arbiter parks on an agent that was last granted the internal

address bus, disabling a parked agent using the IBACR does not take effect

immediately. The IBACR disable bit is observed by the internal address arbiter only

when an agent arbitrates for the internal address bus.

Note:

The data initiators cannot be disabled.

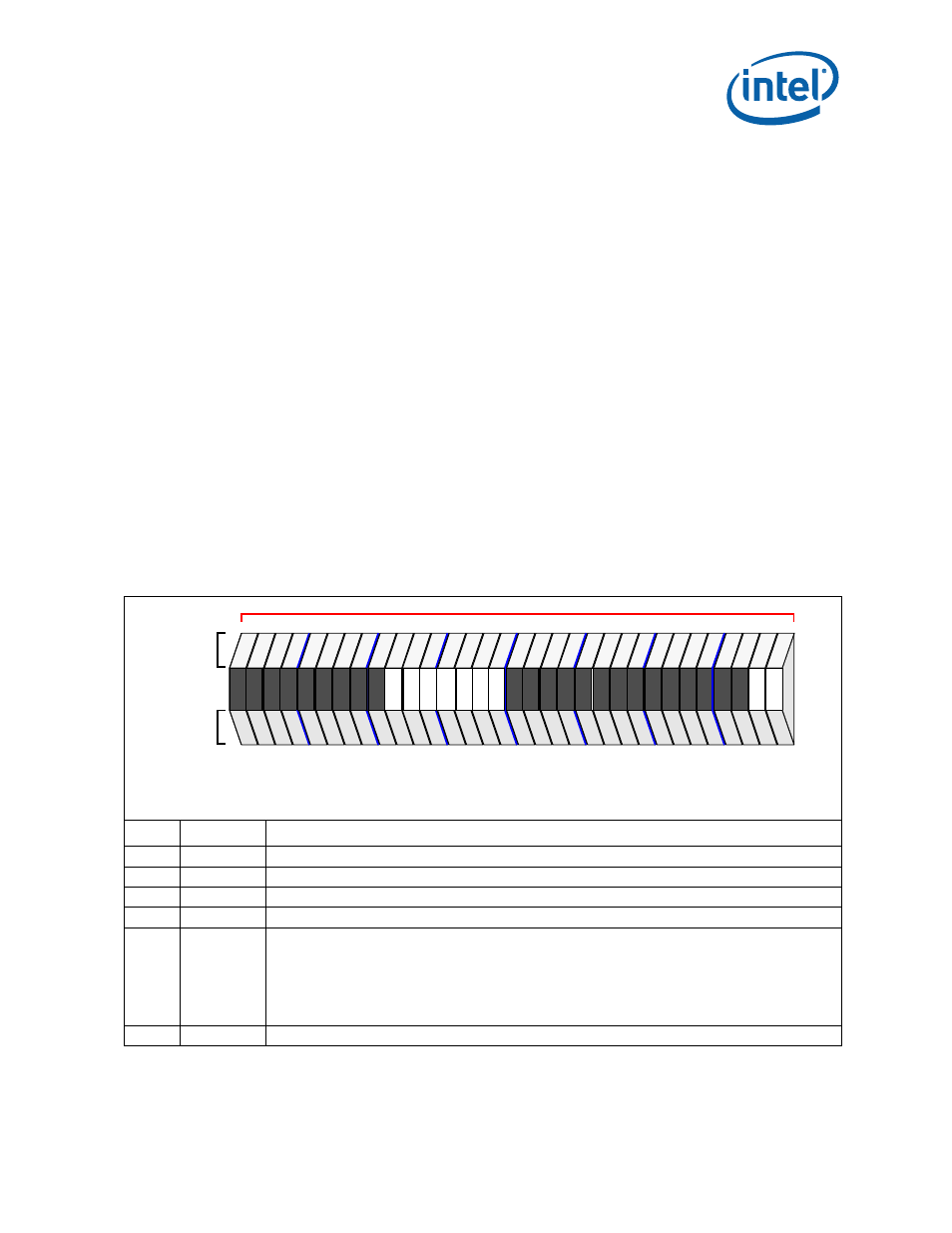

Table 334. Internal Bus Arbitration Control Register — IBACR (Sheet 1 of 2)

Bit

Default

Description

31:25

00H

Reserved.

24

0

2

Reserved.

23

0

2

Reserved.

22

0

2

Reserved.

21

0

2

DDRMCU/MU Group Control — this bit controls the MU initiator. The MU address initiator is not granted

the south internal address bus when this bit is set.

0 = Enabled

1 = Disabled

Note:

The LMU acts as an internal bus address initiator only for issuing MSI or MSI-X writes to the

ATUE or ATUX. Otherwise, the MU is a target device on the internal bus, which are accessed by

the Cores or indirectly by the PCI Host via the ATUs.

20

0

2

Reserved.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rw

na

rw

na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

South XBG

internal bus address offset

+1640H