Pci interface error control and status register, Intel, Bit default description – Intel CONTROLLERS 413808 User Manual

Page 392

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

392

Order Number: 317805-001US

3.17.115 PCI Interface Error Control and Status Register - PIE_CSR

This register indicates whether or not the ATU has detected and logged a PCI interface

error. The register is also used to enabled the logging of additional errors. For more

details, see

Section 3.9, “ATU Error Conditions” on page 270

.

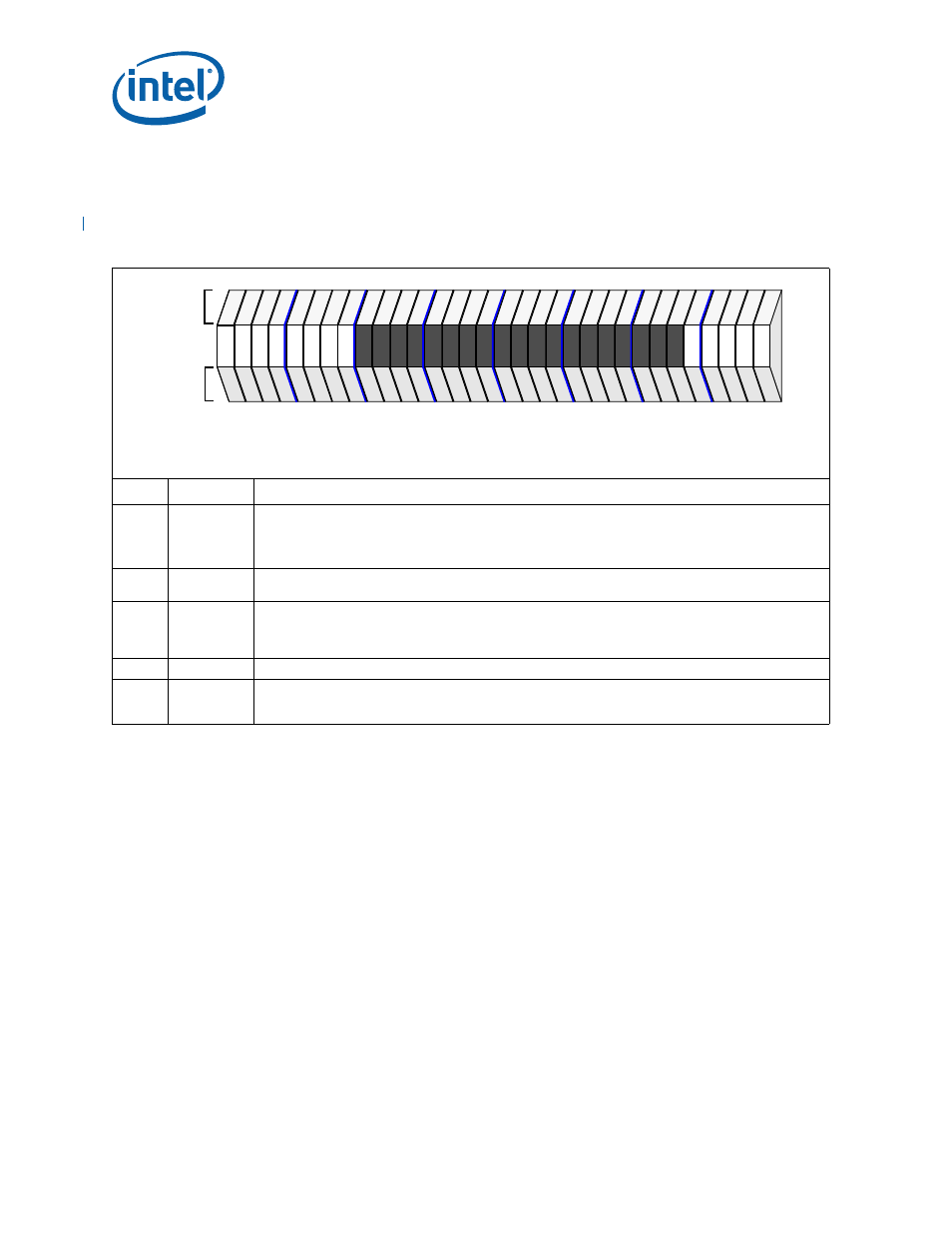

Table 255. PCI Interface Error Control and Status Register - PIE_CSR

Bit

Default

Description

31:28

0000

2

Initiator ID - When the PCI Interface Error First Error Pointer (bits 4:0 of this register) is valid, this field

Indicates the initiator associated with the detected PCI interface error.

“0000” is used to denote inbound requests where the IOP was the completer of the transaction.

See Internal Bus Requester IDs in the System Controller chapter for remaining details of Initiator ID.

27

0

General Device Error (GDE) - This bit is set when an error can not be isolated to a single function and is

being logged against all function.

26:24

000

2

PCI Function Number - When PCIECSR bit 0 is set, this field indicates the 4138xx device function

number that this error is associated with.

Note:

When the General Device Error bit is set then the value in this field is undefined and should be

ignored.

23:5

0

Reserved

4:0

0 0000

PCI Interface Error First Error Pointer - Identifies the bit position of the first error reported in the

Interface Error Status - PIE_STS

register.

Note:

This register does not update until all the bits in the PIE_STS register are cleared.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+380H