19 atu subsystem vendor id register - asvir, Table 45. atu subsystem vendor id register - asvir, 20 atu subsystem id register - asir – Intel CONTROLLERS 413808 User Manual

Page 161: Table 46. atu subsystem id register - asir, 19atu subsystem vendor id register - asvir, 20atu subsystem id register - asir, 45 atu subsystem vendor id register - asvir, 46 atu subsystem id register - asir, Address translation unit (pci-x)—intel, Bit default description

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

161

Address Translation Unit (PCI-X)—Intel

®

413808 and 413812

2.14.19 ATU Subsystem Vendor ID Register - ASVIR

ATU Subsystem Vendor ID Register bit definitions adhere to PCI Local Bus Specification,

Revision 2.3.

2.14.20 ATU Subsystem ID Register - ASIR

ATU Subsystem ID Register bit definitions adhere to PCI Local Bus Specification,

Revision 2.3.

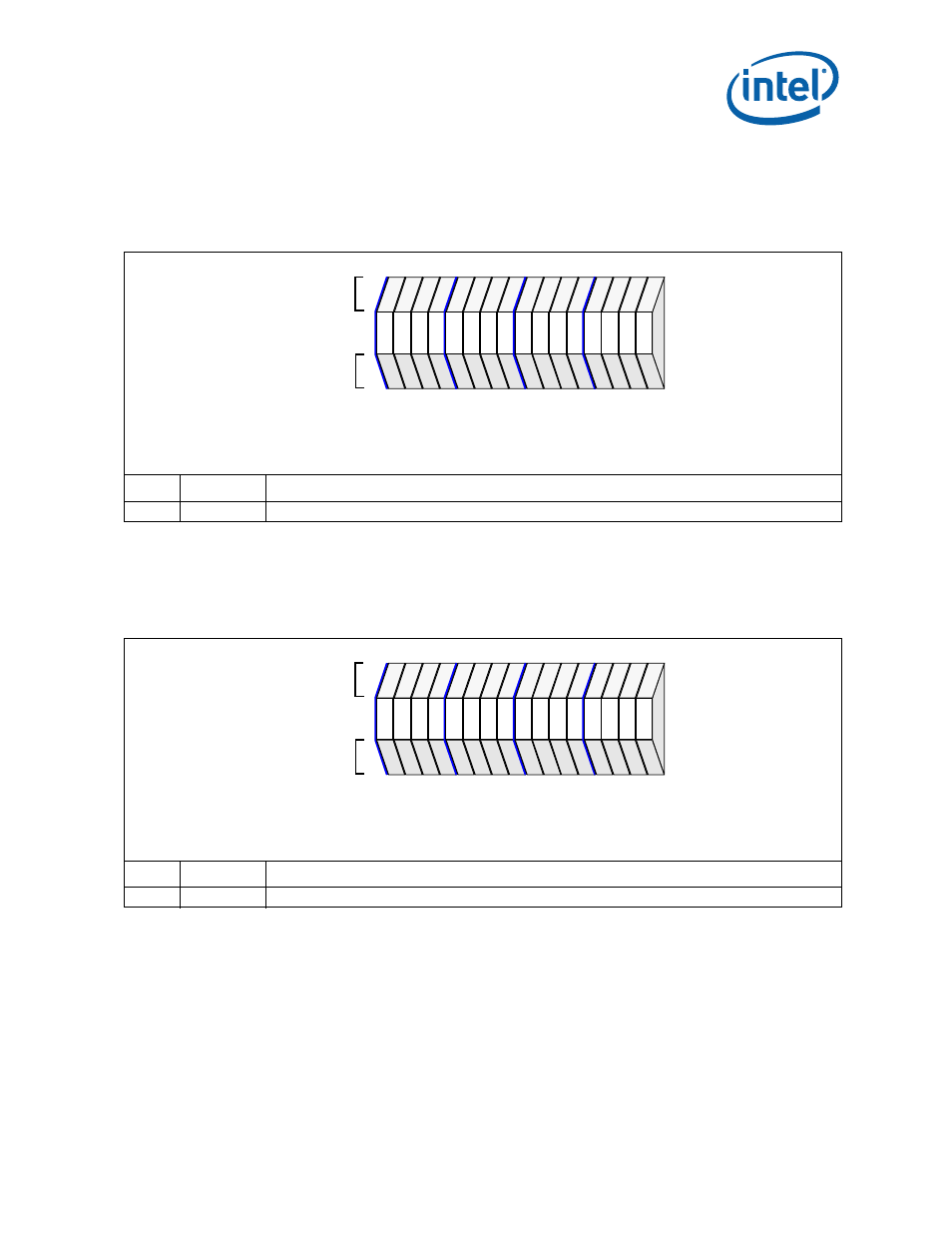

Table 45. ATU Subsystem Vendor ID Register - ASVIR

Bit

Default

Description

15:0

0000H

Subsystem Vendor ID - This register uniquely identifies the add-in board or subsystem vendor.

PCI

IOP

Attributes

Attributes

15

12

8

4

0

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

+02CH

Table 46. ATU Subsystem ID Register - ASIR

Bit

Default

Description

15:0

0000H

Subsystem ID - uniquely identifies the add-in board or subsystem.

PCI

IOP

Attributes

Attributes

15

12

8

4

0

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

+02EH