81 root error status register, Table 221. root error status register - rerr_sr, 81root error status register – Intel CONTROLLERS 413808 User Manual

Page 363: 221 root error status register - rerr_sr, Root error status register - rerr_sr, Address translation unit (pci express)—intel, Bit default description

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

363

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

3.17.81 Root Error Status Register

When operating as the root complex of the PCI Express domain, the Root Error Status

Register reports the status of error messages received by the ATU, and of errors

detected by the ATU. Each correctable and uncorrectable (FATAL/NONFATAL) error

source has a first error bit and a next error bit. When an error is received by the ATU,

the respective first error bit is set and the Requester ID is logged in the Error Source

Identification Register. This register is updated regardless of the settings of the Root

Control register and the Root Error Command registers.

Note:

All bits in this register are sticky through reset.

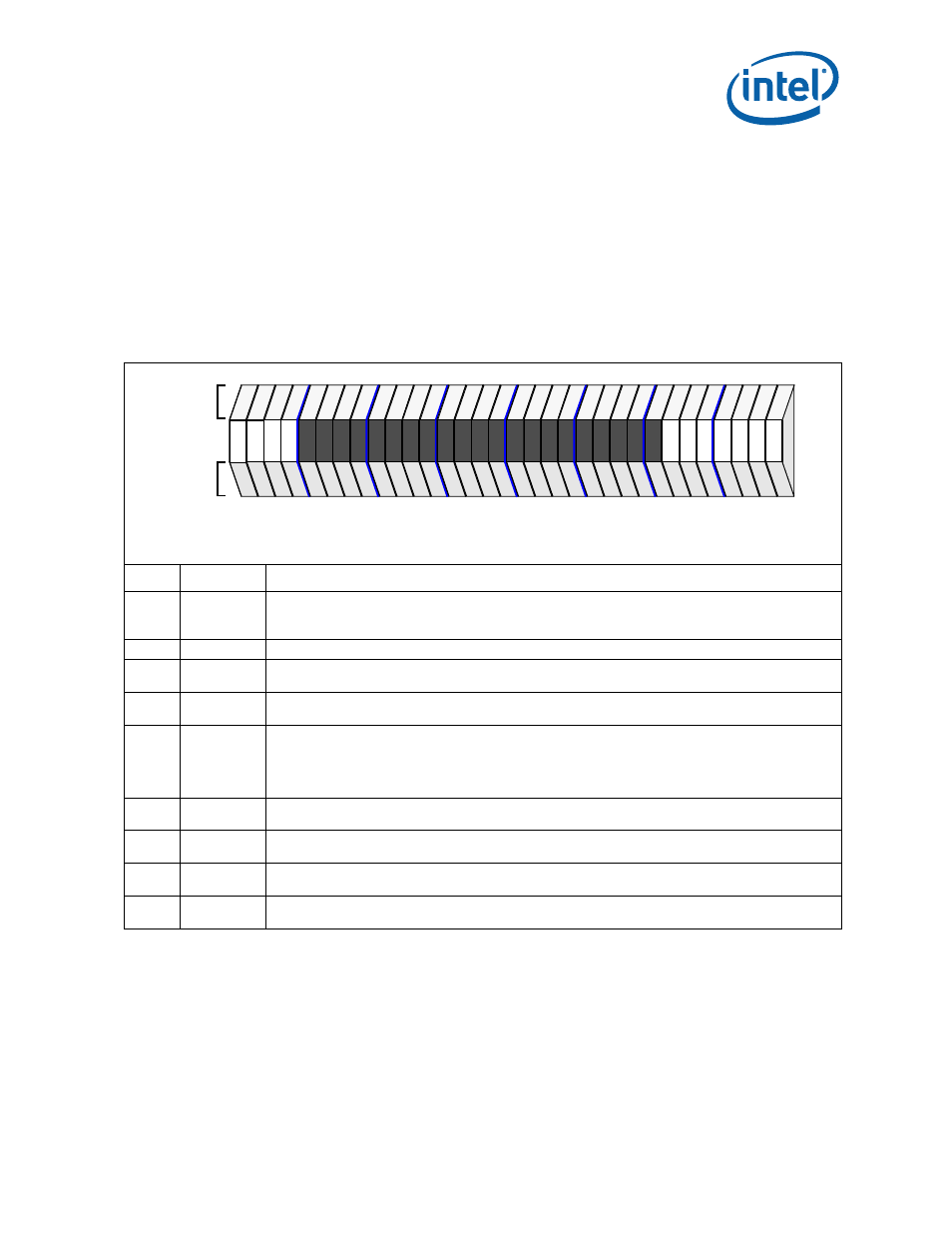

Table 221. Root Error Status Register - RERR_SR

Bit

Default

Description

31:27

0

Advanced Error Interrupt Message Number

The ATU signals these interrupts internally to the Intel XScale

®

processor.

This field is hard-wired to 0.

26:7

00 0000H Reserved

6

0

Fatal Error Message Received

This bit set when one or more Fatal Uncorrectable error messages have been received

5

0

Non-Fatal Error Messages Received

This bit set when one or more Non-Fatal Uncorrectable error messages have been received

4

0

First Uncorrectable Fatal

This bit records the type of the first ERR_FATAL/NONFATAL message.

0 = Indicates the first Uncorrectable Error is NONFATAL

1 = Indicates the first Uncorrectable Error is FATAL

Note:

This bit is only valid when the ERR_FATAL/NONFATL Received bit is set.

3

0

Multiple ERR_FATAL/NONFATAL Received

Set when a correctable error message is received and the ERR_FATAL/NONFATAL bit is already set.

2

0

ERR_FATAL/NONFATAL Received

Set when a correctable error message is received and this bit is not already set.

1

0

Multiple ERR_COR Received

Set when a correctable error message is received and the ERR_COR bit is already set.

0

0

ERR_COR Received

Set when a correctable error message is received and this bit is not already set.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

ro

ro

ro

ro

ro

ro

ro

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rv

ro

rc

rc

rc

rc

rc

rc

rc

rc

rc

rc

rc

rc

rc

rc

S

S S S

S

S S S

S

S S

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+130H