4 timer registers, Table 418. timer registers, 1 power up/reset initialization – Intel CONTROLLERS 413808 User Manual

Page 633: Table 419. timer power up mode settings, 418 timer registers, 419 timer power up mode settings

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

633

Timers—Intel

®

413808 and 413812

11.4

Timer Registers

As shown in

, each timer has three co-processor registers:

• Timer Mode Register — programs the specific mode of operation or indicates the

current programmed status of the timer. This register is described in

11.4.2, “Timer Mode Registers – TMR0:1” on page 634

• Timer Count Register — contains the timer’s current count. See

“Timer Count Register – TCR0:1” on page 637

.

• Timer Reload Register — contains the timer’s reload count. See

“Timer Reload Register – TRR0:1” on page 637

.

11.4.1

Power Up/Reset Initialization

Upon assertion of P_RST#, the timer registers are initialized to the values shown in

.

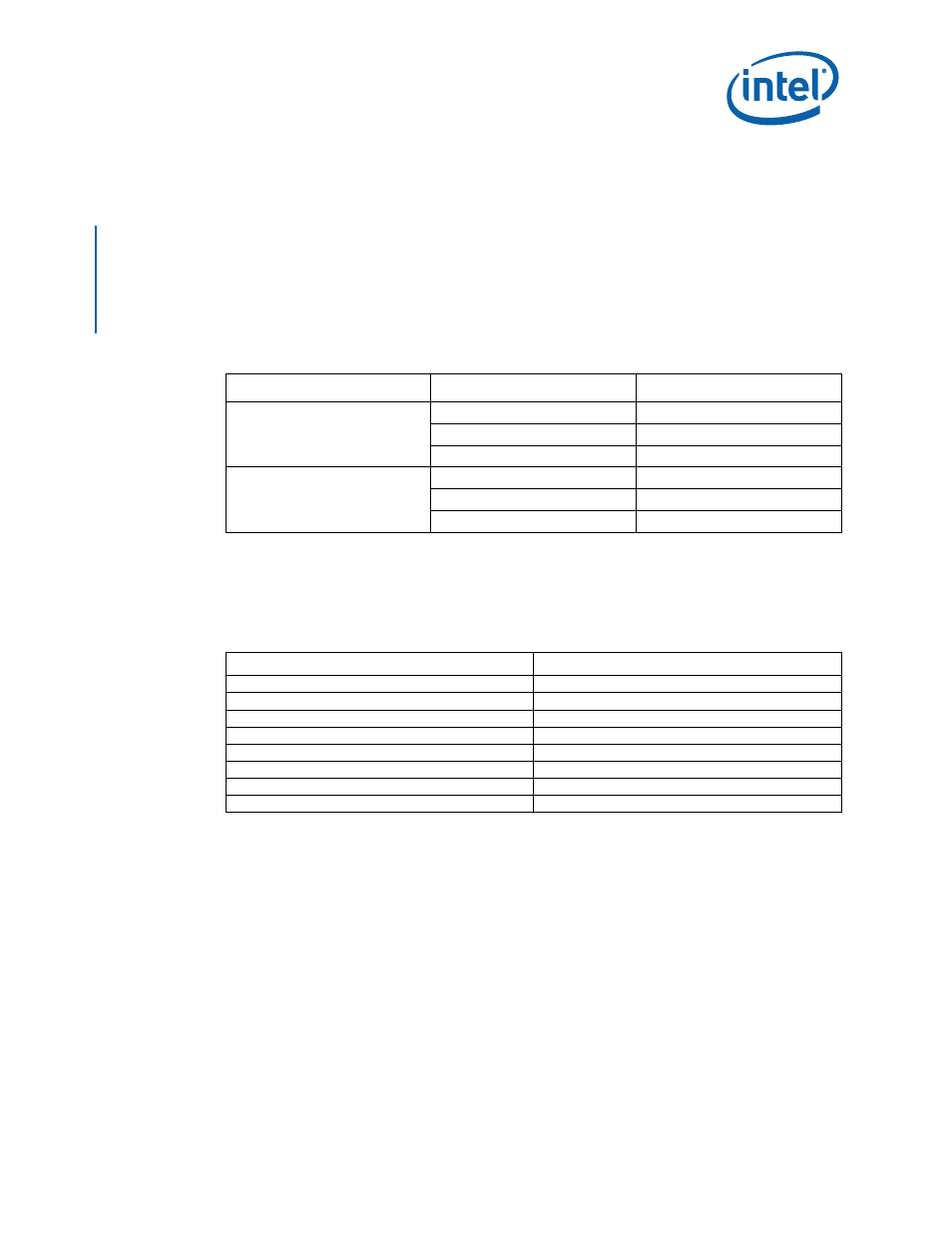

Table 418. Timer Registers

Timer Unit

Register Acronym

Register Name

Timer 0

TMR0

Timer Mode Register 0

TCR0

Timer Count Register 0

TRR0

Timer Reload Register 0

Timer 1

TMR1

Timer Mode Register 1

TCR1

Timer Count Register 1

TRR1

Timer Reload Register 1

Table 419. Timer Power Up Mode Settings

Mode/Control Bit

Notes

TMRx.tc = 0

No terminal count

TMRx.enable = 0

Prevents counting and assertion of TINTx

TMRx.reload = 0

Single terminal count mode

TMRx.pri = 0

Privileged Mode and User Mode Writes Allowed

TMRx.csel1:0 = 0

Timer Clock = internal bus clock

TCRx.d31:0 = 0

Undefined

TRRx.d31:0 = 0

Undefined

TINTx output

Deasserted