Interrupt controller unit—intel, Xint13, Xint12 – Intel CONTROLLERS 413808 User Manual

Page 601: Xint11, Xint10, Xint9, Xint8, Bit default description

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

601

Interrupt Controller Unit—Intel

®

413808 and 413812

05

0

2

XINT13#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

04

0

2

XINT12#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

03

0

2

XINT11#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

02

0

2

XINT10#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

01

0

2

XINT9#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

00

0

2

XINT8#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

Table 396. Interrupt Steering Register 1 — INTSTR1 (Sheet 2 of 2)

Bit

Default

Description

Memory

Coprocessor

Attributes

Attributes

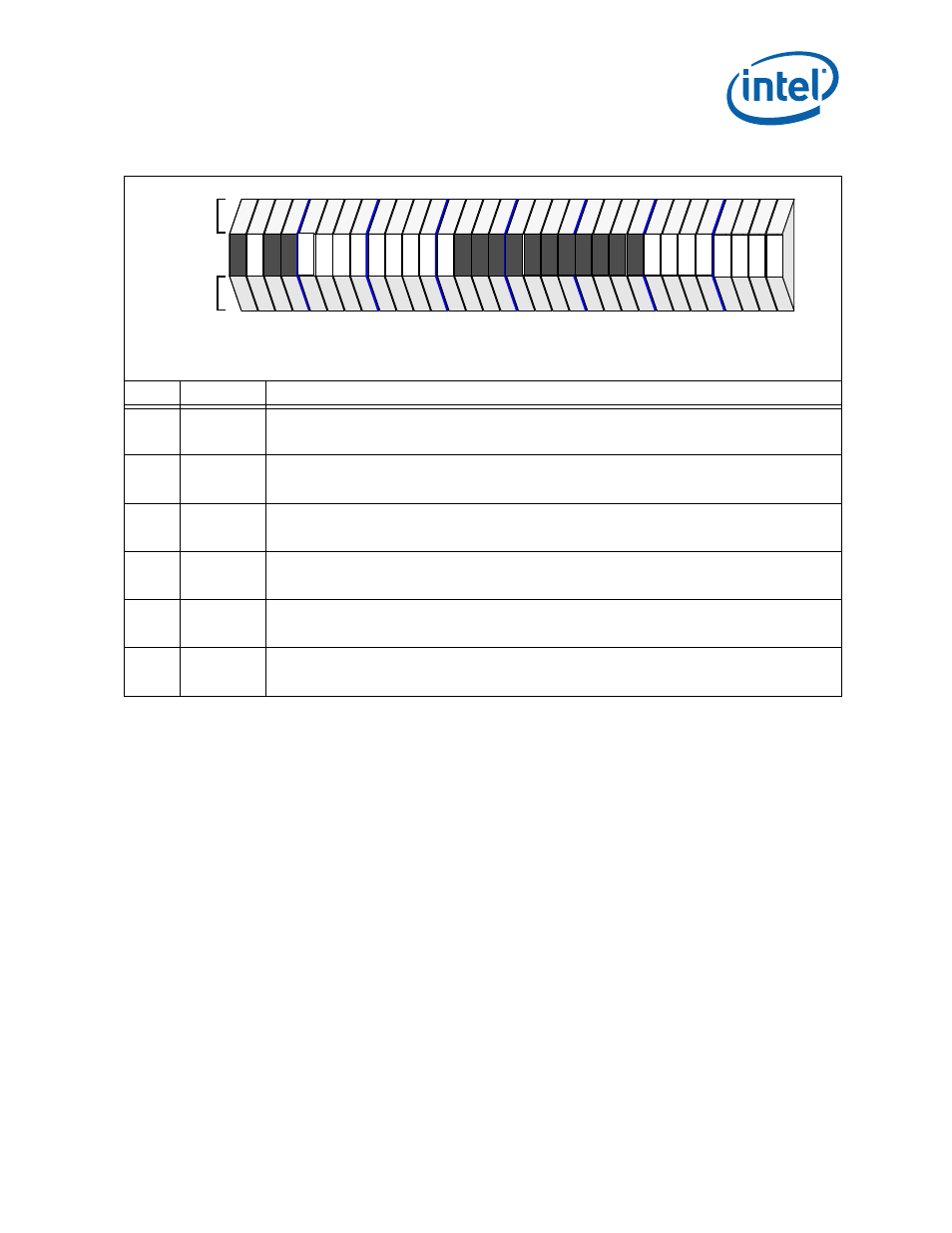

28

24

20

16

12

8

4

0

31

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Intel XScale

®

processor Coprocessor

address

CP6, Page 5, Register 1