3 architecture – Intel CONTROLLERS 413808 User Manual

Page 647

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

647

SMBus Interface Unit—Intel

®

413808 and 413812

12.3.3

Architecture

The 4138xx SMBus register interface consists of a set of registers that are only

accessible from the SMBus interface only and are shown in

and

These registers are used to issue commands for reading and writing configuration

registers and memory locations on 4138xx

shows that register format for

accessing configuration space.

shows the register format for accessing

memory space, The command register provides a bit that indicates whether

configuration or memory space ought to be accessed.

All SMBus accesses to internal register space are initiated via a write to the command

register (CMD). The command register indicates the access type (read or write) and

whether the command is targeting the configuration spaces or memory-mapped

registers. Any register writes received by the 4138xx while a command is already in

progress receive a NAK to prevent spurious operation. The master is no longer

expected to poll the CMD register to prevent overwriting the current command in

progress prior to issuing further writes. The SMBus access is delayed by stretching the

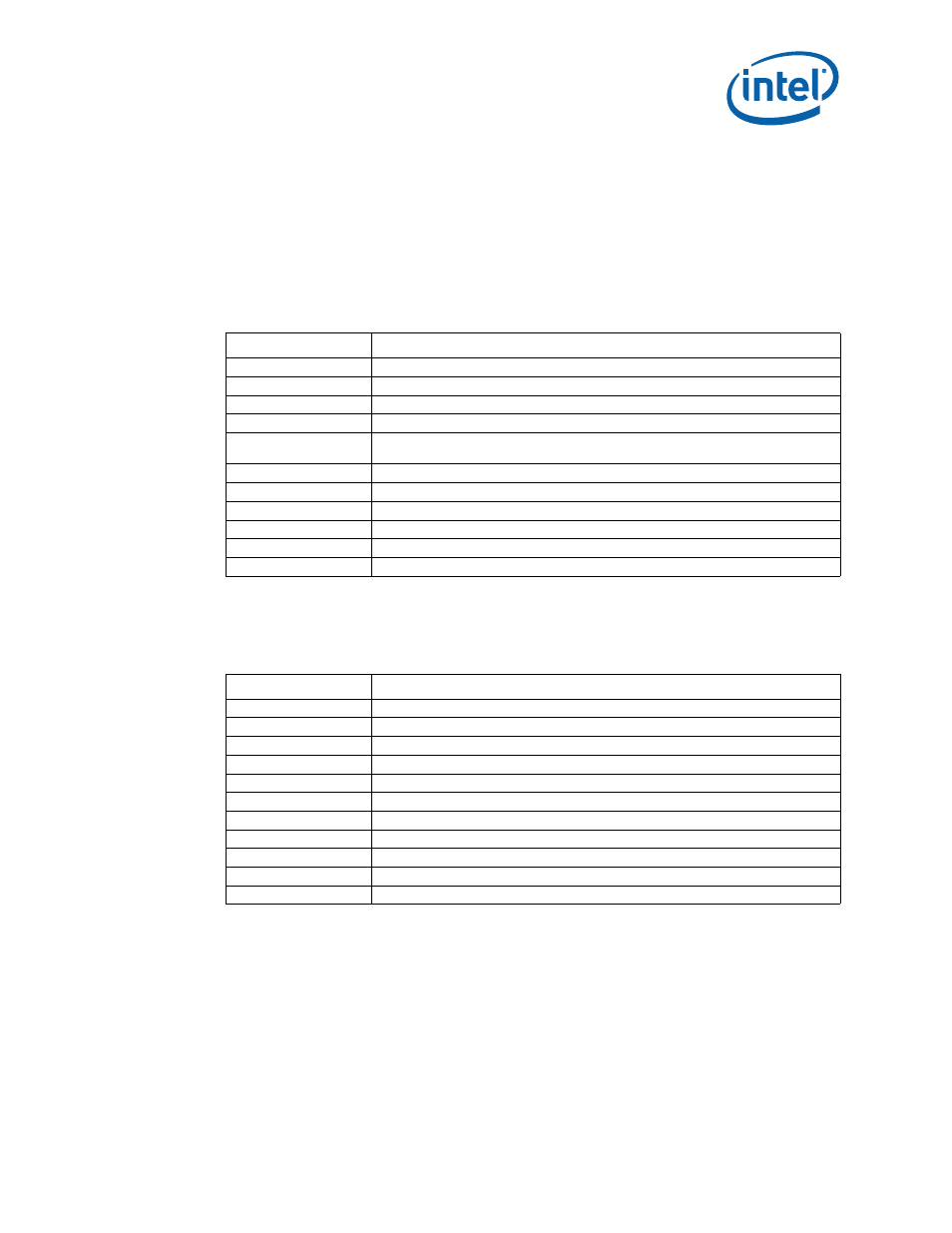

Table 430. SMBus Interface Registers for Configuration Space Access

Register

Name and Function

CMD

Command

BYTCNT

Byte Count

ADDR3

Bus Number

a

a. The ADDR3 field is ignored as Bus Number is not applicable for 4138xx.

ADDR2

Device/Function Number.

b

b. Only ADDR2[2:0] are used to select a Function Number. ADDR2[7:3] are ignored as Device Number is not

applicable to 4138xx.

ADDR1

Extended Register Number — only bits [3:0]. The extended register allows access

to 4-KByte configuration space.

ADDR0

Register Number — offset into function configuration space

DATA3

Data[31:24] — fourth byte of data.

DATA2

Data[23:16] — third byte of data.

DATA1

Data[15:8] — second byte of data.

DATA0

Data[7:0] — first byte of data.

STS

Status, only for reads.

Table 431. SMBus Interface Registers for Memory Space Access

Register

Name and Function

CMD

Command

BYTCNT

Byte Count

ADDR3

Destination Memory.

a

a. The ADDR3 field is ignored on 4138xx as only the Memory-Mapped Register block are accessible as a memory

space.

ADDR2

Address Offset — bits[23:16].

b

b. Only ADDR2[2:0] are used on 4138xx. ADDR2[7:3] are ignored as the Memory-Mapped Register Block only

occupies 512 KBytes of memory space.

ADDR1

Address Offset — bits[15:8].

ADDR0

Address Offset — bits[7:0].

DATA3

Data[31:24] — fourth byte of data.

DATA2

Data[23:16] — third byte of data.

DATA1

Data[15:8] — second byte of data.

DATA0

Data[7:0] — first byte of data.

STS

Status, only for reads.