3 pmon status register 0-7 - pmon_sts[0:7, Pmon, X counter – Intel CONTROLLERS 413808 User Manual

Page 754: Intel, Bit default description

Intel

®

413808 and 413812—PMON Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

754

Order Number: 317805-001US

16.5.6.3 PMON Status Register 0-7 - PMON_STS[0:7]

This 32-bit register reports the current status of the

PMON

x counter.

Table 494. PMON Status Register 0-7 - PMON_STS[0:7] (Sheet 1 of 2)

Bit

Default

Description

31

0b

Decrement Event Indicator (IEI)

0 = The selected decrement event was NOT detected.

1 =

1

= The selected decrement event WAS detected.

This bit is updated every clock, whether or not the counter is counting.

30

0b

Increment Event Indicator (IEI)

0 = The selected increment event was NOT detected.

1 =

1

= The selected increment event WAS detected.

This bit is updated every clock, whether or not the counter is counting.

29

0b

Counter Active Indicator (CAI)

0 = The associated counter is in a state that does NOT allow it to be incremented or decremented when

the appropriate event(s) are detected.

1 = The associated counter is in a state that allows it to be incremented or decremented when the

appropriate event(s) are detected.

This bit is updated every clock.

28

0b

In Use

Software Mutex bit

• After a full component RESET, a read to this bit returns a 0

• After the first read, subsequent reads return a 1

• A write of a 1 to this bit resets the next read value to 0

• Writing a 0 to this bit has no effect

Software can poll this bit until it reads a 0, and then owns the usage of the corresponding counter. This

bit has no other effect on any

PMON

Counter registers, and is only used as a semaphore among

various independent software threads that may need to utilize this performance counter. Software that

reads this register, but does not intend to claim exclusive access, must write a 1 to this bit (when it

reads a 0), in order to allow other software threads to claim it. This bit is particularly useful when

supporting multi-threaded environments.

Attribute is Read Set/Write Clear (RS/WC)

27

0b

Unsupported Event Indicator (UEI)

0 = No unsupported events have been selected.

1 = An unsupported Event Selection Code (ESC) was written into in one of the event selection fields

(Command Trigger, Increment Event, or Decrement Event).

26

0b

Overflow/Underflow Indicator (OUI)

0 = The associated 32 bit counter has NOT rolled over since the last time it was cleared.

1 = The associated 32 bit counter HAS rolled over since the last time it was cleared.

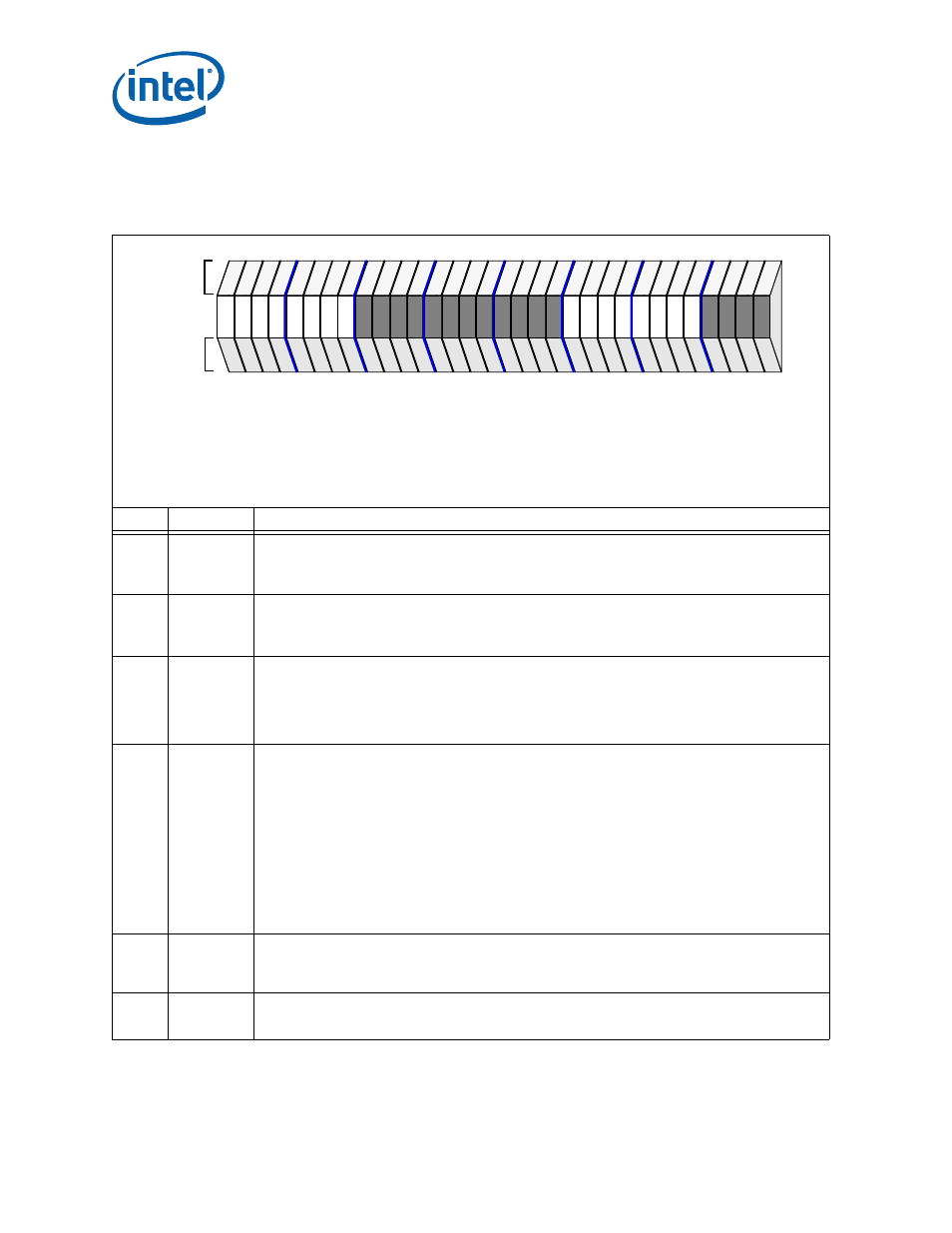

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rc

rc

rc

rc

ro

ro

sc

sc

rc

rc

rc

rc

rc

rc

rc

rc

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

rv

rv

rv

rv

rv

rv

rv

rv

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

SC = Read Set/Write Clear

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

PMON

_STS0

PMON

_STS1

PMON

_STS2

PMON

_STS3

PMON

_STS4

PMON

_STS5

PMON

_STS6

PMON

_STS7

+008h

+018h

+028h

+038h

+048h

+058h

+068h

+078h