12 atu bist register - atubistr, Table 151. atu bist register - atubistr, 12atu bist register - atubistr – Intel CONTROLLERS 413808 User Manual

Page 303: 151 atu bist register - atubistr, Atu bist register - atubistr, Address translation unit (pci express)—intel, Bit default description

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

303

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

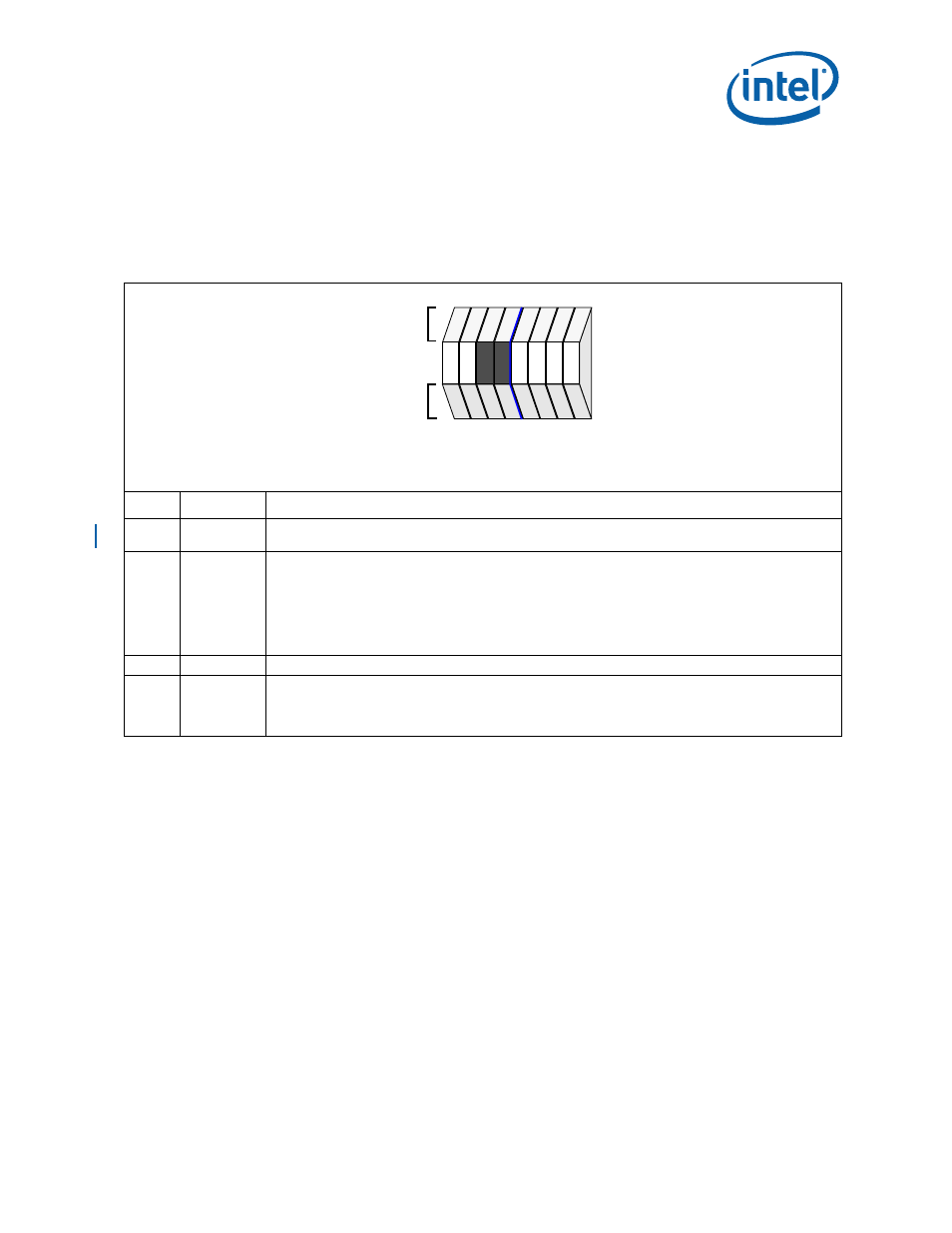

3.17.12 ATU BIST Register - ATUBISTR

The ATU BIST Register controls the functions the Intel XScale

®

processor performs

when BIST is initiated. This register is the interface between the host processor

requesting BIST functions and the 4138xx replying with the results from the software

implementation of the BIST functionality.

Table 151. ATU BIST Register - ATUBISTR

Bit

Default

Description

07

0

2

BIST Capable - This bit value is always equal to the ATUCR ATU BIST Interrupt Enable bit. See

3.17.40, “ATU Configuration Register - ATUCR” on page 326

.

06

0

2

Start BIST - When the ATUCR BIST Interrupt Enable bit is set:

Setting this bit generates an interrupt to the Intel XScale

®

processor to perform a software BIST

function. The Intel XScale

®

processor clears this bit when the BIST software has completed with the

BIST results found in ATUBISTR register bits [3:0].

When the ATUCR BIST Interrupt Enable bit is clear:

Setting this bit does not generate an interrupt to the Intel XScale

®

processor and no BIST functions is

performed. The Intel XScale

®

processor does not clear this bit.

05:04

00

2

Reserved

03:00

0000

2

BIST Completion Code - when the ATUCR BIST Interrupt Enable bit is set and the ATUBISTR Start BIST

bit is set (bit 6):

The Intel XScale

®

processor places the results of the software BIST in these bits. A nonzero value

indicates a device-specific error.

PCI

IOP

Attributes

Attributes

7

4

0

ro

ro

rw

rw

rv

rv

rv

rv

rw

rw

rw

rw

rw

rw

rw

rw

Internal Bus Address Offset

+00FH

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible