4 ecc interrupts/error conditions, Table 348. smcu error response, 348 smcu error response – Intel CONTROLLERS 413808 User Manual

Page 531: Section, Section 8.4, “ecc interrupts/error

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

531

SRAM Memory Controller—Intel

®

413808 and 413812

8.4

ECC Interrupts/Error Conditions

The SMCU has two ECC conditions which require intervention from the Intel XScale

®

processor. If a single-bit error is detected during a read cycle, the SMCU can correct

the data returned but software needs to fix the error in the memory array. If a multi-bit

error is detected, the core decides how to handle the condition. For all ECC errors, the

SMCU records the requester of the transaction resulting in the error in SELOG[23:16]

and interrupts the core.

If the SMCU detects an ECC error during a read or write cycle, SMCISR[0] is set to 1.

Whenever the SMCU toggles the SMCISR[0] bit from 0 to 1, an interrupt is generated

to the core.

shows how the SMCU responds to error conditions.

Note:

If ECC reporting is enabled with SECCR[1] or SECCR[0] and an ECC error occurs,

SMCISR[0] is set and SELOG/SECAR/SECUAR logs the error in addition to

actions.

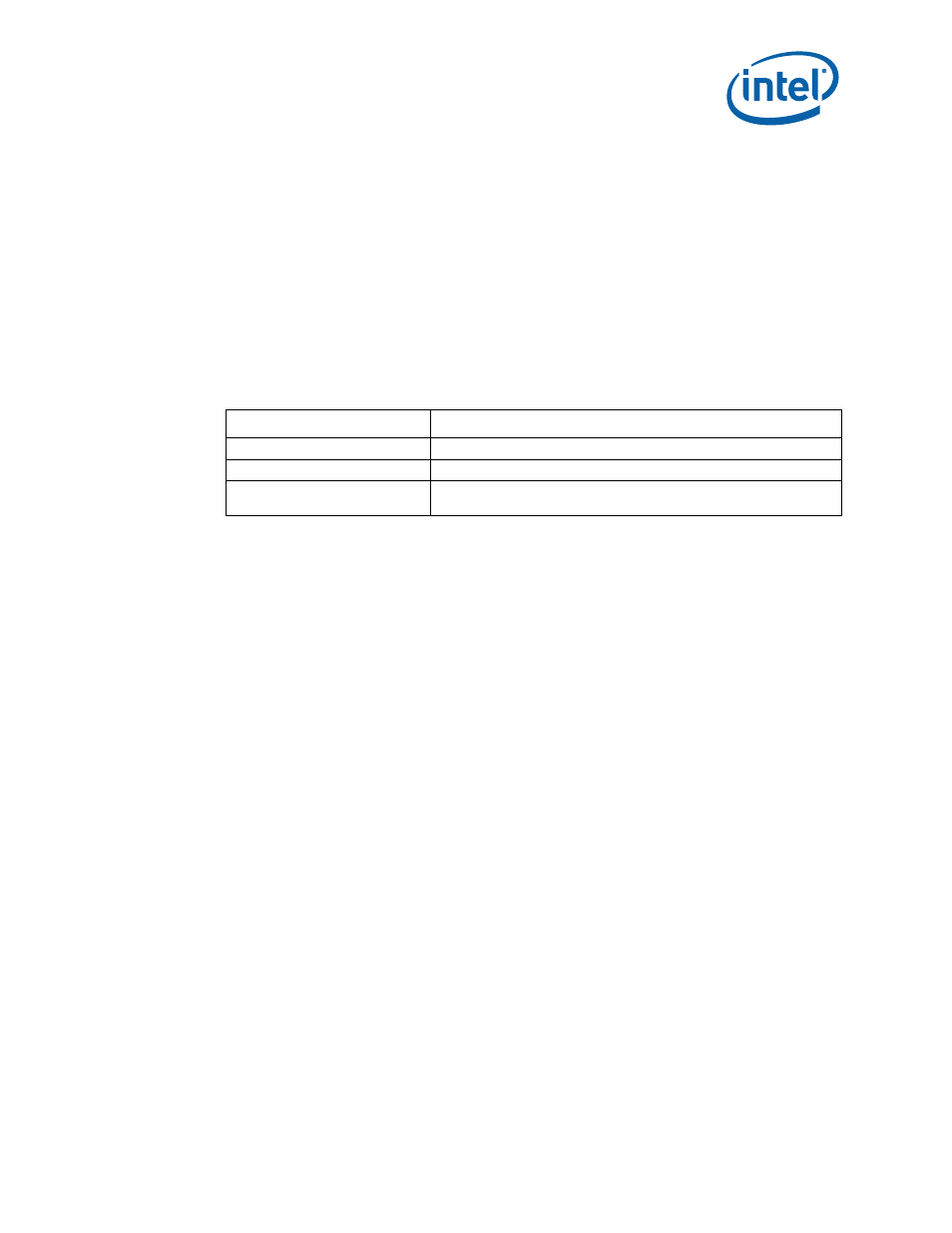

Table 348. SMCU Error Response

Error Type

SMCU Action

Single-Bit during a read or write

Fix Error (if ECC error correction enabled in the SECCR)

Multi-bit during a read

Target Abort the Internal Bus transaction

Multi-bit during a write

New ECC is generated with bad data and written to SRAM array. Data

location is no longer valid.