Equation 9. inbound translation, Figure 25. inbound translation example, 25 inbound translation example – Intel CONTROLLERS 413808 User Manual

Page 239

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

239

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

Once the transaction is claimed, the upper 32-bits of the address is discarded and the

lower 32-bits of the address must be translated from a PCI address to a 36-bit internal

bus address. The algorithm is:

The lower 32-bits of the incoming PCI address are first bitwise ANDed with the bitwise

inverse of the limit register. This result is bitwise ORed with the ATU Translate Value,

which is then ORed with the 4-bit ATU Upper Translate Value left shifted by 32; the

result is the 36-bit internal bus address. This translation mechanism is used for all

inbound memory read and write commands excluding inbound configuration read and

writes. Inbound configuration cycle translation is described in

“Inbound Configuration Cycle Translation (ID Routed)” on page 242

.

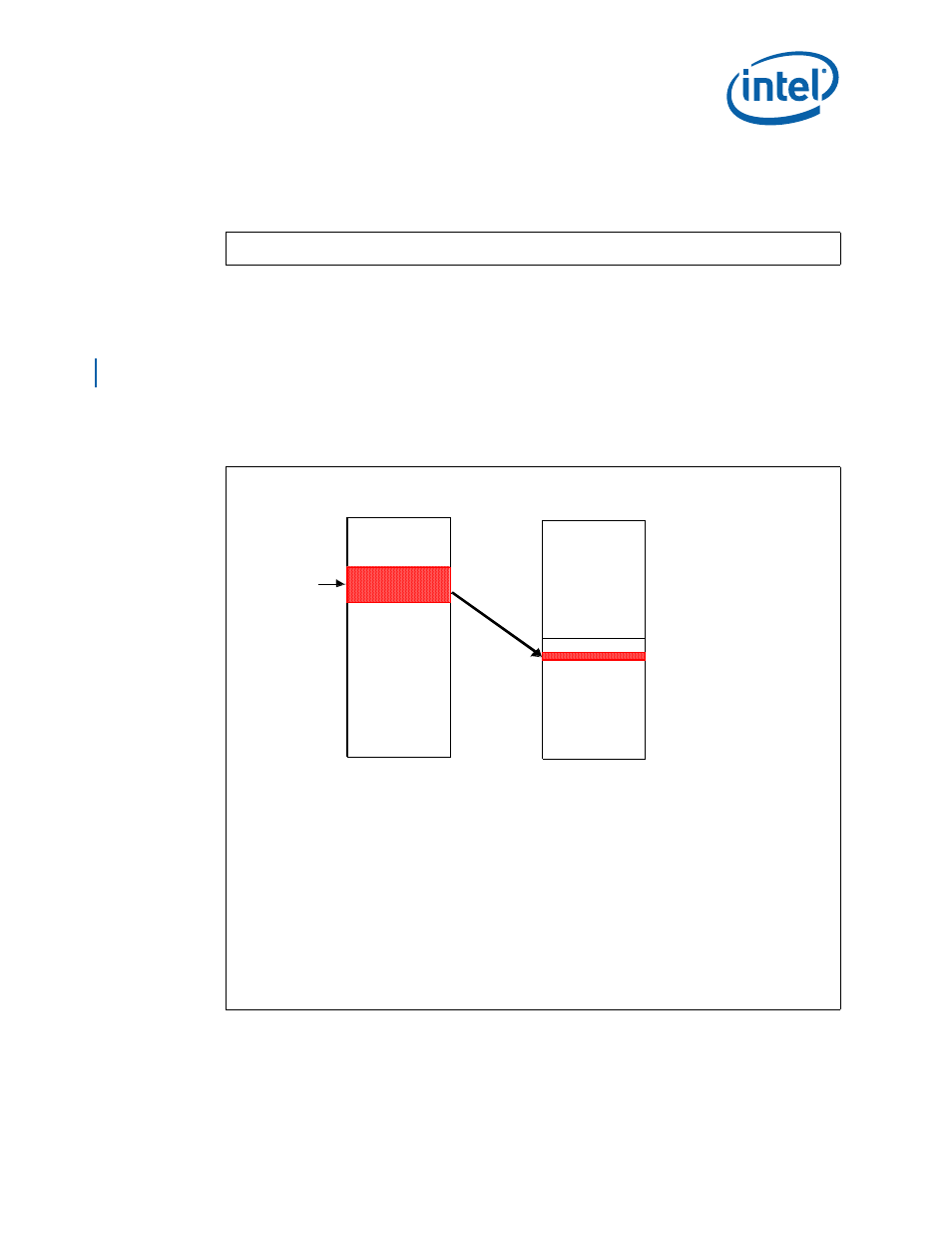

shows an inbound translation example for 32-bit addressing. This example

would hold true for an inbound transaction from PCI Express Link.

Equation 9. Inbound Translation

4138xx Internal Bus Address = ((PCI_Address[31:0] & ~Limit_Register[31:0]) |

ATU_Translate_Value_Register[31:0]) | (ATU_Upper_Translate Value_Register[3:0] << 32).

Figure 25. Inbound Translation Example

0000 0000H

FFFF FFFFH

0 0000 0000H

F FFFF FFFFH

Base_Register = 3A00 0000H

Limit_Register = FF80 0000H (8 Mbyte limit value)

Inbound

Window

Inbound Translation Window ranges from 3A00 0000H to 3A7F FFFFH (8 Mbytes)

PCI_Address

Value_Register = B100 0000H

Internal_Bus

Address

PCI Address

Space

I/O Processor Local

Memory Address Space

Address Detection (32-bit address)

PCI_Address and Limit_Register == Base_Register

3A45 012CH and FF80 0000H == 3A00 0000H

3A45 012CH

PCI_Address is in the Inbound Translation Window

Address Translation

IB_Address = (PCI_Address and ~Limit_Register) | Value_Register

IB_Address = ((3A45 012CH and 007F FFFFH) | B100 0000H) | (1H << 32)

1 B145 012CH

Register Values

IB_Address = 1 B145 012CH

Upper_Value_Register = 1H

Translation

B6323-01