3 timer state diagram, Figure 72. timer unit state diagram, 72 timer unit state diagram – Intel CONTROLLERS 413808 User Manual

Page 632: Intel

Intel

®

413808 and 413812—Timers

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

632

Order Number: 317805-001US

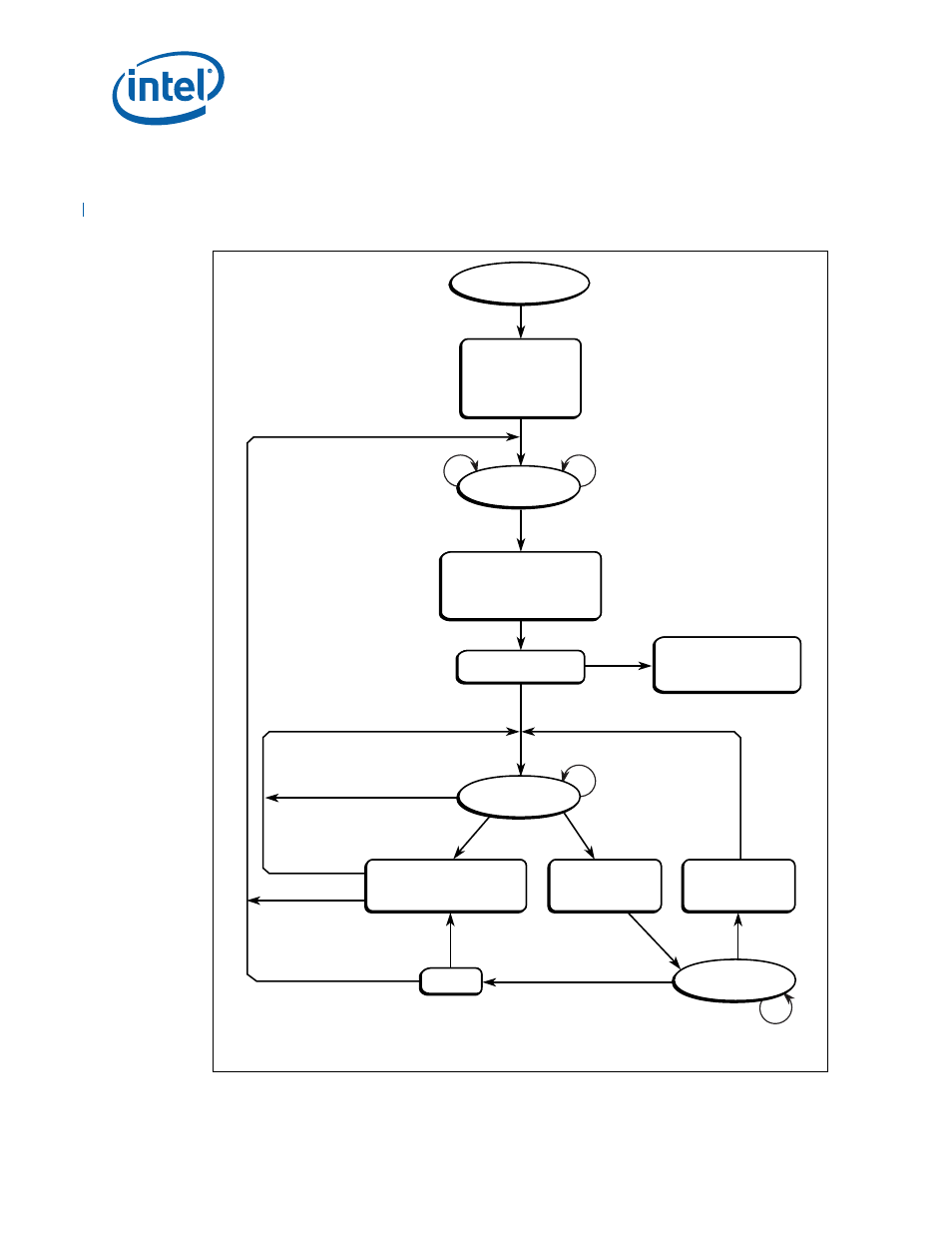

11.3

Timer State Diagram

shows the common states of the Timer Unit. For uncommon conditions see

Section 11.5, “Uncommon TCRX and TRRX Conditions” on page 640

Figure 72. Timer Unit State Diagram

A6770-01

TMRx.enable = 0

TMRx.reload = 0

TMRx.pri = 0

TMRx.csel1:0 = 0

IPND.tip = 0

TMRx.enable = 1

TMRx.reload = user value

TMRx.pri = user value

TMRx.csel1:0 = user value

TMRx.reload = user value

TMRx.pri = user value

TMRx.csel1:0 = user value

TC = 1

IPND.tip = 1

TMRx.enable = 0

TC = 0

TMRx.enable = 1

TCRx = TRRx

Bus Clock

"Uncommon TCRX and

TRRX Conditions"

Hardware / Software

Reset

Initial TCRx Check

TC = 0

Bus Clock or SW Read

SW Write (TMRx.enable = 1

SW Write

(TMRx.enable = 0)

Clock Unit Tick

and TCRx != 0

TCRx=0

TMRx.enable = 0

SW Read

SW Write

SW Read

TMRx.enable = 1

SW Read/Write & Reload = 0

IDLE

TCRx != 0

TCRx = 0

SW Write

Reload = 1

Decrement

TCRx

TC Detected

State