2 outbound interrupts, Table 378. interrupt output pin descriptions, 378 interrupt output pin descriptions – Intel CONTROLLERS 413808 User Manual

Page 571: Xint[3:0, P_int[d:a, Message registers, Doorbell registers

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

571

Interrupt Controller Unit—Intel

®

413808 and 413812

10.4.2

Outbound Interrupts

When 4138xx is setup as an endpoint device with the PCI-X interface, the

XINT[3:0]#

pins act as output pins (

P_INT[D:A]#

) respectively. The Messaging Unit (MU) and the

TPMI functions have the capability of generating interrupts on the PCI interrupt output

pins. The MU has two distinct messaging mechanisms. Each allows a host processor or

external PCI agent and the 4138xx to communicate through message passing and

interrupt generation. The two mechanisms are:

•

Message Registers

— allow the 4138xx and external PCI agents to communicate

by passing messages in one of four 32-bit Message Registers. In this context, a

message is any 32-bit data value. Message registers combine aspects of mailbox

registers and doorbell registers. Writes to the message registers may optionally

cause interrupts.

•

Doorbell Registers

— allow the 4138xx to assert the PCI interrupt signals and

allow external PCI agents to generate an interrupt to the Intel XScale

®

processor.

Both mechanisms can result in Outbound Interrupts to a host processor.

Refer to the Host Interface and TPMI Chapter for detailed descriptions of the TPMI

Outbound Interrupts.

The external interrupt output interface for 4138xx consists of the pins shown in

.

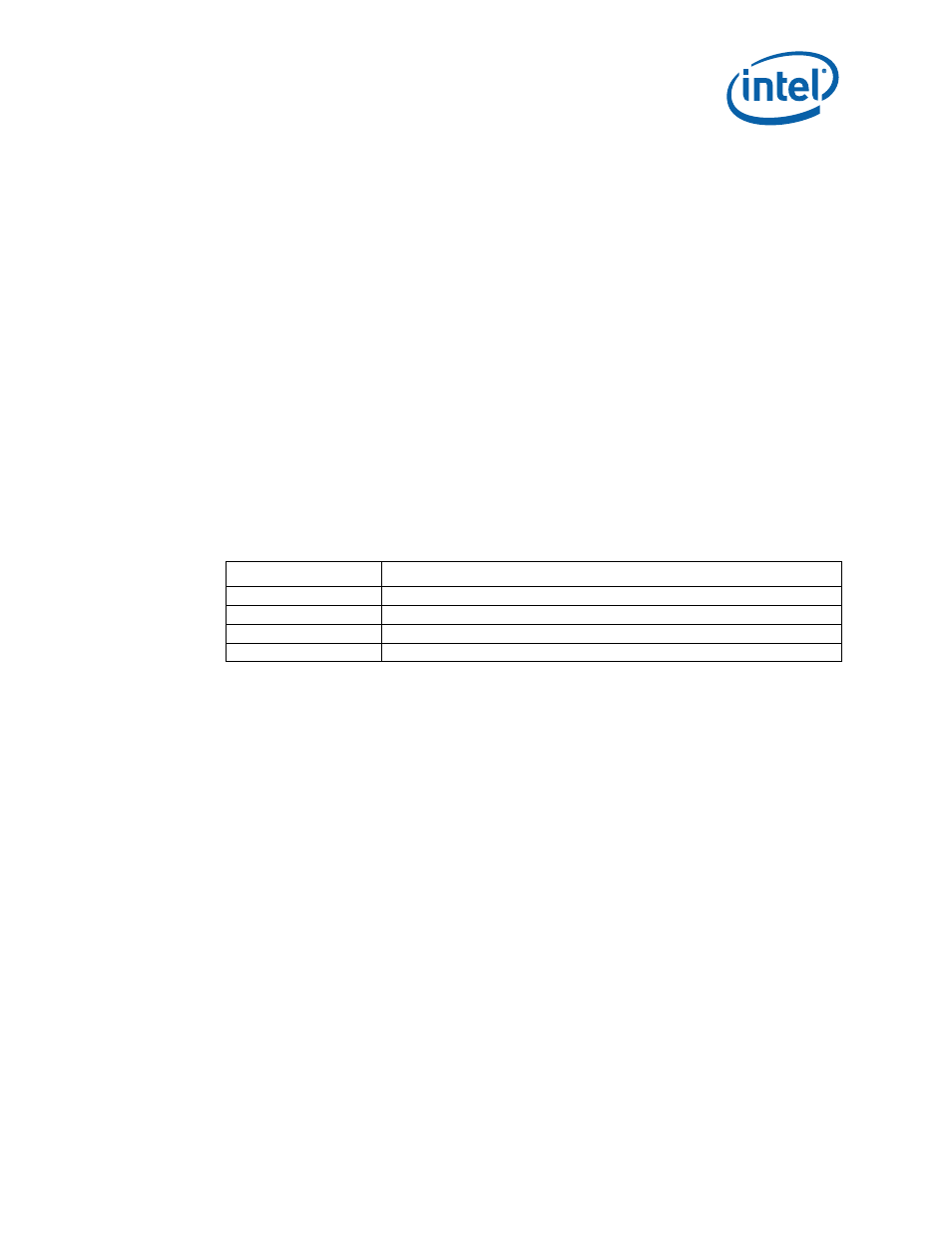

Table 378. Interrupt Output Pin Descriptions

Signal

Description

P_INTA#

Primary PCI Interrupt output of 4138xx source from the MU.

P_INTB#

Primary PCI Interrupt output of 4138xx

source from the MU.

P_INTC#

Primary PCI Interrupt output of 4138xx

source from the MU.

P_INTD#

Primary PCI Interrupt output of 4138xx

source from the MU.