4 inbound interrupt status register - iisr, 269 inbound interrupt status register - iisr, Inbound interrupt status register – Intel CONTROLLERS 413808 User Manual

Page 414: Iisr, Intel, Bit default description

Intel

®

413808 and 413812—Messaging Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

414

Order Number: 317805-001US

4.7.4

Inbound Interrupt Status Register - IISR

The Inbound Interrupt Status Register (IISR) contains hardware interrupt status. It

records the status of Intel XScale

®

processor interrupts generated by the Message

Registers, Doorbell Registers, and the Circular Queues. All interrupts are routed to the

Normal Messaging Unit interrupt input of the Intel XScale

®

processor, except for the

Error Doorbell Interrupt and the Outbound Free Queue Full interrupt; these two are

routed to the Messaging Unit Error interrupt input. The generation of interrupts

recorded in the Inbound Interrupt Status Register may be masked by setting the

corresponding bit in the Inbound Interrupt Mask Register. Some of the bits in this

register are Read Only. For those bits, the interrupt must be cleared through another

register.

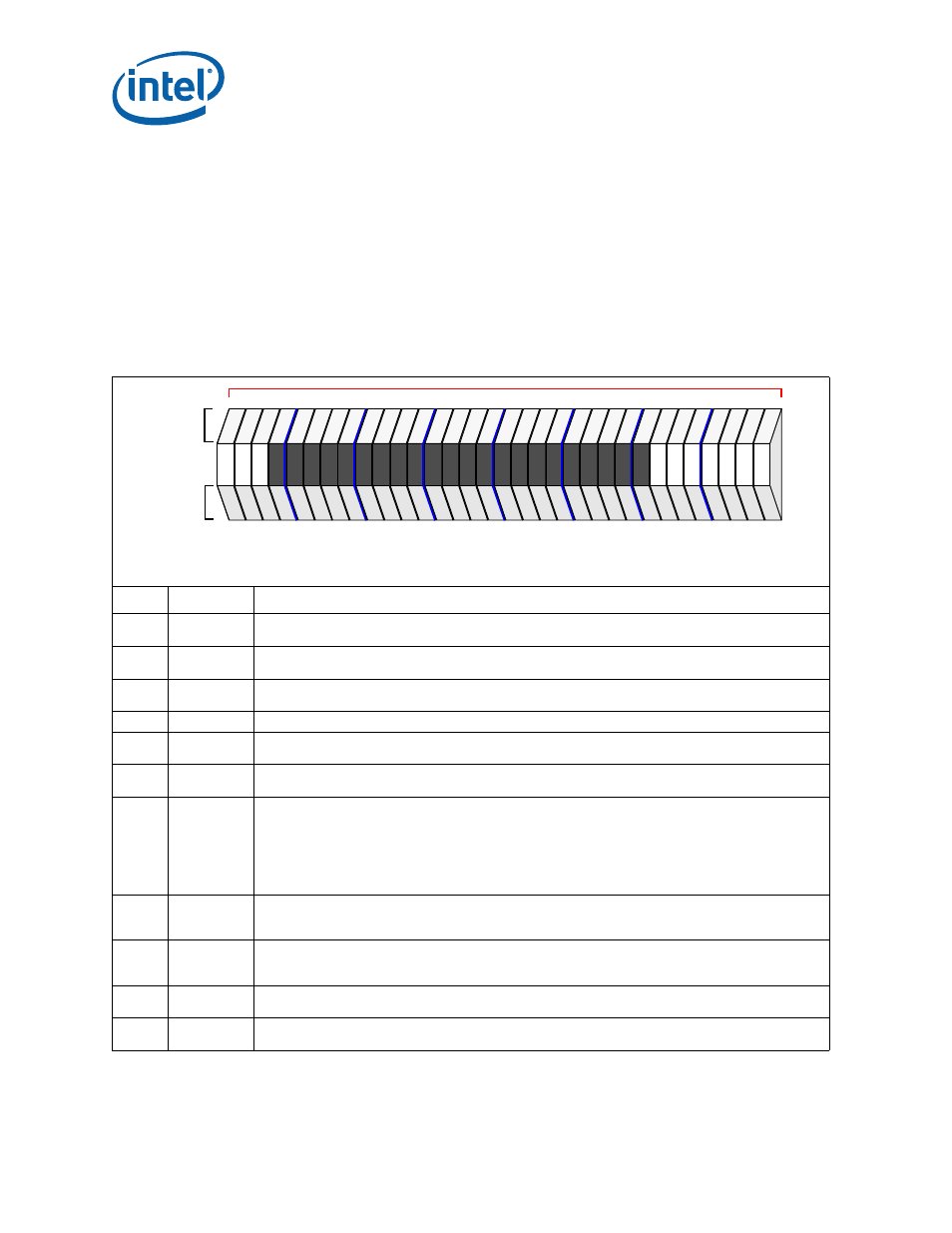

Table 269. Inbound Interrupt Status Register - IISR

Bit

Default

Description

31

0

2

Coordinated Reset Interrupt - This bit is set when the Coordinated Reset bit (bit 1) is set in the Inbound

Reset Control and Status Register.

30

0

2

Selective Reset Interrupt - This bit is set when the Selective Reset bit (bit 0) is set in the Inbound Reset

Control and Status Register.

29

0

2

MU MSI-X Table Write Interrupt - This bit is set when a write occurs to any of the MU MSI-X Table entry.

When set, this bit results in the assertion of the MU MSI-X Table Write Interrupt.

28:07

0000000H Reserved

06

0

2

Index Register Interrupt - This bit is set by the MU hardware when an Index Register has been written

after a Host I/O Interface transaction.

05

0

2

Outbound Free Queue Full Interrupt - This bit is set when the Outbound Free Head Pointer becomes

equal to the Tail Pointer and the queue is full. An Error interrupt is generated for this condition.

04

0

2

Inbound Post Queue Interrupt - This bit is set by the MU hardware when the Inbound Post Queue has

been written. Once cleared, an interrupt is NOT generated when the head and tail pointers remain

unequal (i.e. queue status is Not Empty). Therefore, when software leaves any unprocessed messages

in the post queue when the interrupt is cleared, software must retain the information that the Inbound

Post queue status is not empty.

Note:

This interrupt is provided with dedicated support in the 4138xx Interrupt Controller.

03

0

2

Error Doorbell Interrupt - This bit is set when the Error Interrupt of the Inbound Doorbell Register is set.

To clear this bit (and the interrupt), the Error Interrupt bit of the Inbound Doorbell Register must be

clear.

02

0

2

Inbound Doorbell Interrupt - This bit is set when at least one Normal Interrupt bit in the Inbound

Doorbell Register is set. To clear this bit (and the interrupt), the Normal Interrupt bits in the Inbound

Doorbell Register must all be clear.

01

0

2

Inbound Message 1 Interrupt - This bit is set by the MU hardware when the Inbound Message 1 Register

has been written.

00

0

2

Inbound Message 0 Interrupt - This bit is set by the MU hardware when the Inbound Message 0 Register

has been written.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

ro

ro

ro

ro

rc

rc

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rc

rc

rc

rc

rc

ro

ro

ro

ro

ro

rc

rc

rc

rc

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

MU/PCI Base Address Offset

IISR: 0024H

internal bus address offset

IISR: 4024H