Intel, P_serr, Perr – Intel CONTROLLERS 413808 User Manual

Page 182: Bit default description, Reserved. 04 0, Detected - set when, Is detected on the pci bus by the atu. 03 0, Itself or the atu observed

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

182

Order Number: 317805-001US

07

0

2

Internal Bus Master Abort - set when a transaction initiated by the ATU internal bus initiator interface

ends in a Master-abort.

06:05

00

2

Reserved.

04

0

2

P_SERR#

Detected - set when

P_SERR#

is detected on the PCI bus by the ATU.

03

0

2

PCI Master Abort - set when a transaction initiated by the ATU PCI initiator interface ends in a

Master-abort.

02

0

2

PCI Target Abort (master) - set when a transaction initiated by the ATU PCI master interface ends in a

Target-abort.

01

0

2

PCI Target Abort (target) - set when the ATU interface, acting as a target, terminates the transaction on

the PCI bus with a target abort.

00

0

2

PCI Master Parity Error - Master Parity Error - The ATU interface sets this bit under the following

conditions:

• The ATU asserted

PERR#

itself or the ATU observed

PERR#

asserted.

• And the ATU acted as the requester for the operation in which the error occurred.

• And the ATUCMD register’s Parity Error Response bit is set

• Or (PCI-X Mode Only) the ATU received an Uncorrectable Write Data Error Message

• And the ATUCMD register’s Parity Error Response bit is set

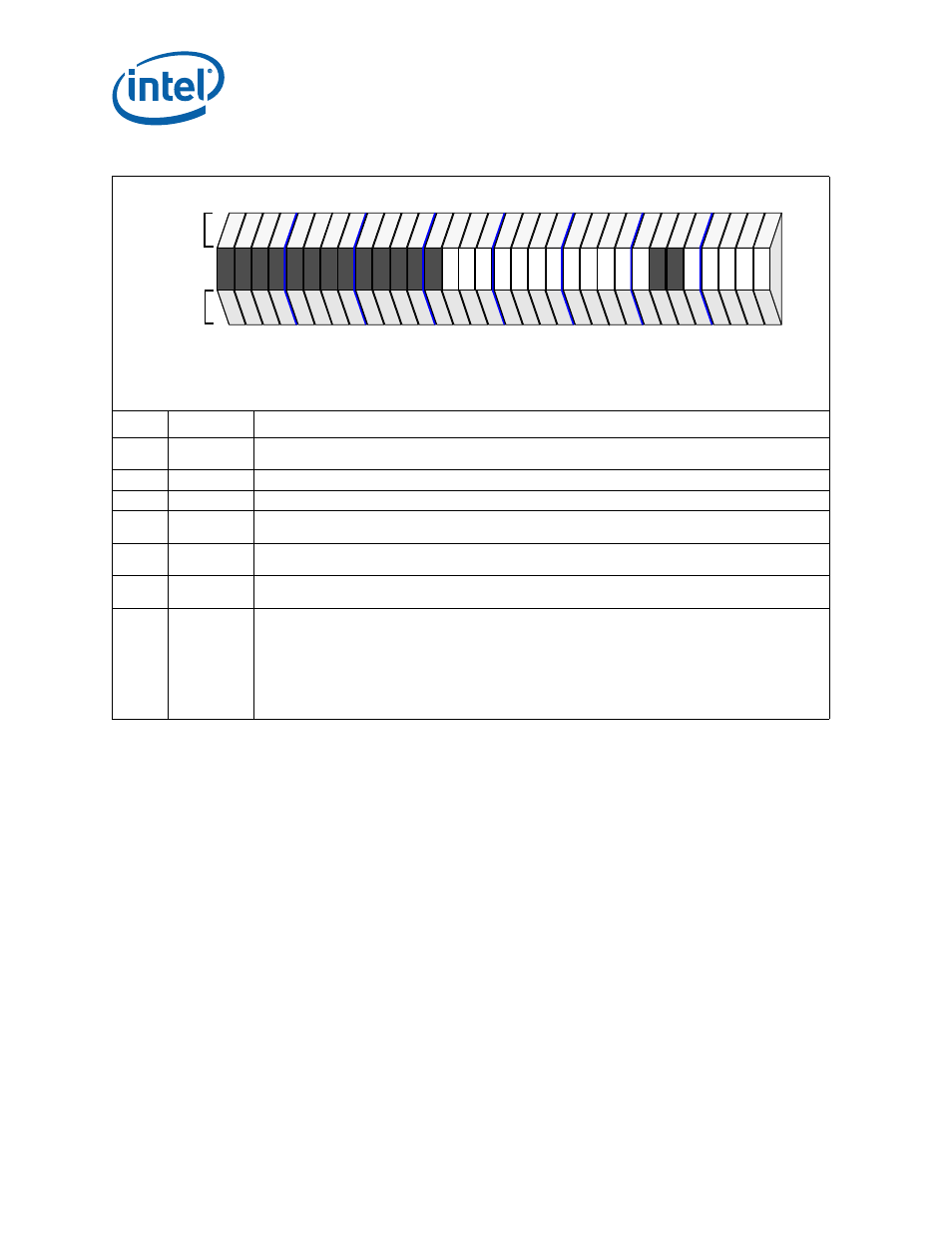

Table 69. ATU Interrupt Status Register - ATUISR (Sheet 2 of 2)

Bit

Default

Description

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rc

ro

rc

ro

rc

ro

rc

ro

rc

ro

rc

ro

rc

ro

rc

ro

rc

ro

rc

ro

rc

ro

rc

ro

rv

rv

rv

rv

rc

ro

rc

ro

rc

ro

rc

ro

rc

ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

+078H