2 host interface units, Table 542. pci function mmr locations, 542 pci function mmr locations – Intel CONTROLLERS 413808 User Manual

Page 809

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

809

Peripheral Registers—Intel

®

413808 and 413812

19.6.2

Host Interface Units

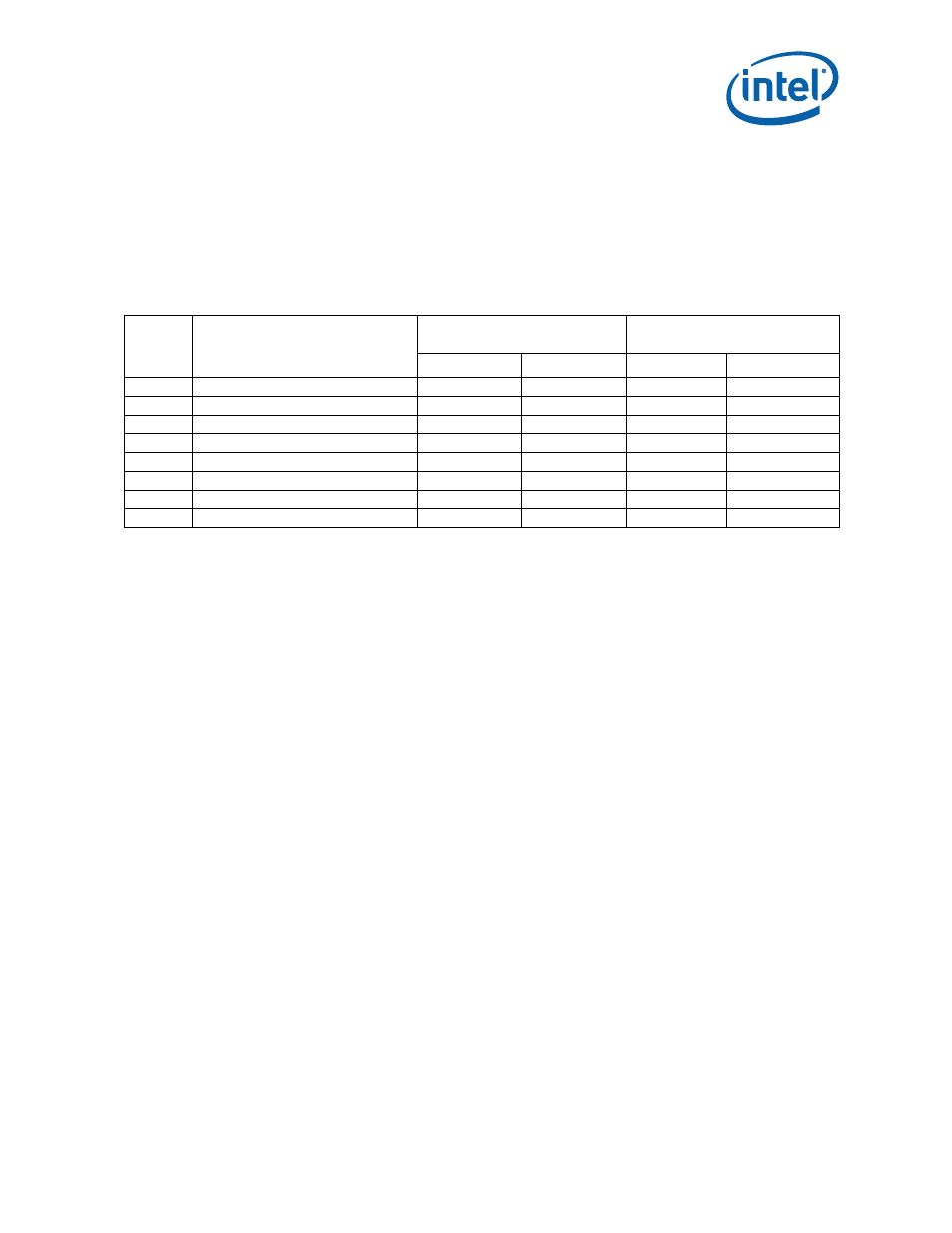

This section describes the register layout of the units that are visible as PCI functions.

These units include the TPMI0-3, ATUE and ATUX. The PCI Function number for each of

these units vary based on strapping options that are sampled during reset.

The PCI Function number associated with each unit and its Base Address Offset are

detailed in

Table 542, “PCI Function MMR Locations”

Table 542. PCI Function MMR Locations

PCI

Function

Number

CONTROLLER_ONLY# = 0

(has priority over

INTERFACE_SEL_PCIX#)

INTERFACE_SEL_PCIX# =

Internal Bus Address Offset

(Relative to PMMRBAR)

0

1

PCI Attributes Local Attributes

0

Reserved

ATUX

ATUE

+4 0000H

+4 8000H

1

Reserved

Reserved

Reserved

+4 1000H

+4 9000H

2

Reserved

Reserved

Reserved

+4 2000H

+4 A000H

3

Reserved

Reserved

Reserved

+4 3000H

+4 B000H

4

ATUX

Reserved

Reserved

+4 4000H

+4 C000H

5

ATUE

ATUE

ATUX

+4 5000H

+4 D000H

6

Reserved

Reserved

Reserved

+4 6000H

+4 E000H

7

Reserved

Reserved

Reserved

+4 7000H

+4 F000H