1 flash read cycle, Figure 65. 120 ns flash single transfer read cycle, 65 120 ns flash single transfer read cycle – Intel CONTROLLERS 413808 User Manual

Page 551: Pce[1:0, D[7:0, And the arrival of data from the flash device on

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

551

Peripheral Bus Interface Unit—Intel

®

413808 and 413812

9.2.6.1

Flash Read Cycle

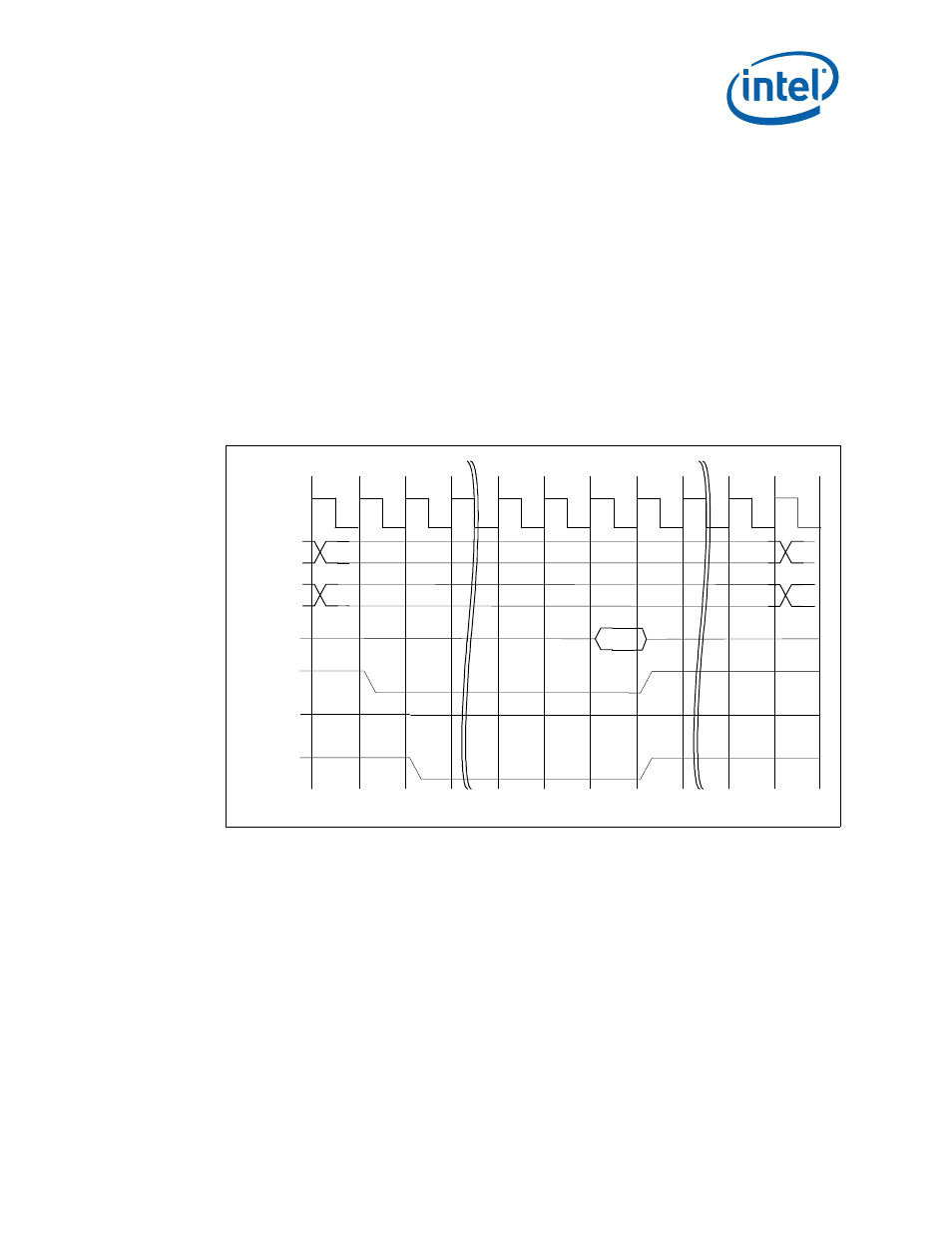

Reading a Flash device involves driving the address, output enable, and chip enable.

Depending on the speed of the Flash device, the data returns several cycles later.

The definition of address-to-data wait states are the number of cycles between the

assertion of

PCE[1:0]#

, and the arrival of data from the Flash device on

D[7:0]

(8-bit

Flash). The definition of recovery wait states are the number of cycles between the

data arrival on

D[7:0]

and the address for the next Peripheral transaction.

Address-to-data and recovery wait states are programmed in PBBAR0 and PBBAR1 and

are identical for reads and writes. Since the read wait state requirement is typically

greater, the write wait state requirement is insured to be met.

illustrates a single read cycle example for a 120 ns Flash device. The number

of wait states used for address-to-data is provided by the Address-to-Data Wait States

field in the PBBARx.

Figure 65. 120 ns Flash Single Transfer Read Cycle

A[24:03]

A[02:00]

Ta2

Tw1

Tw8

Td 2

Tr1

Tr4

POE #

PWE #

PCEx #

D[15:00]

D_in

Ti/Ta

Ta1

Td 1

B6269-01