Intel CONTROLLERS 413808 User Manual

Page 807

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

807

Peripheral Registers—Intel

®

413808 and 413812

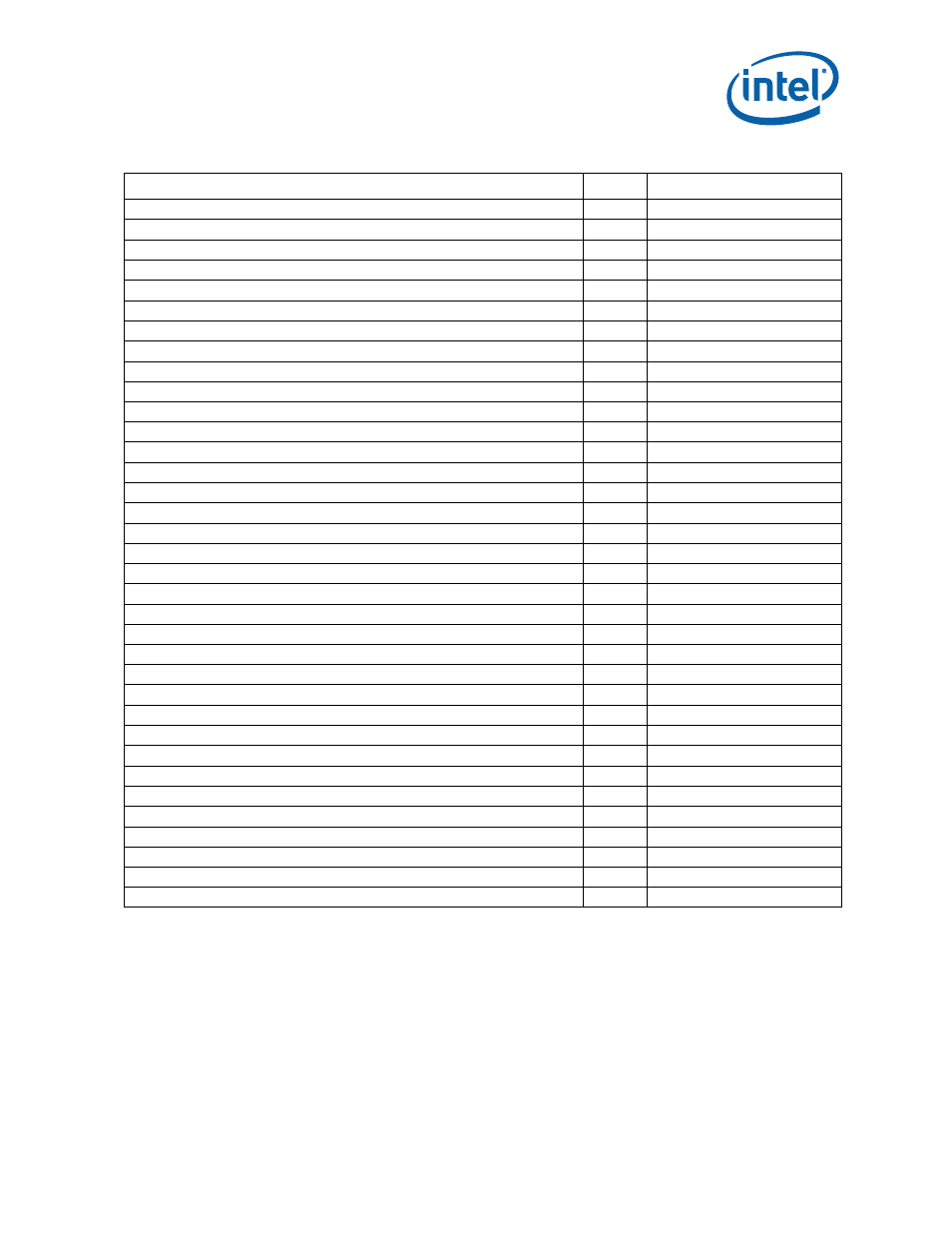

MU MSI-X Table Message Address Register 0 — M_MT_MAR0

32

+1000

MU MSI-X Table Message Upper Address Register 0 — M_MT_MUAR0

32

+1004

MU MSI-X Table Message Data Register 0 — M_MT_MDR0

32

+1008

MU MSI-X Table Message Vector Control Register 0 — M_MT_MVCR0

32

+100C

MU MSI-X Table Message Address Register 1 — M_MT_MAR1

32

+1010

MU MSI-X Table Message Upper Address Register 1 — M_MT_MUAR1

32

+1014

MU MSI-X Table Message Data Register 1 — M_MT_MDR1

32

+1018

MU MSI-X Table Message Vector Control Register 1 — M_MT_MVCR1

32

+101C

MU MSI-X Table Message Address Register 2 — M_MT_MAR2

32

+1020

MU MSI-X Table Message Upper Address Register 2 — M_MT_MUAR2

32

+1024

MU MSI-X Table Message Data Register 2 — M_MT_MDR2

32

+1028

MU MSI-X Table Message Vector Control Register 2 — M_MT_MVCR2

32

+102C

MU MSI-X Table Message Address Register 3 — M_MT_MAR3

32

+1030

MU MSI-X Table Message Upper Address Register 3 — M_MT_MUAR3

32

+1034

MU MSI-X Table Message Data Register 3 — M_MT_MDR3

32

+1038

MU MSI-X Table Message Vector Control Register 3 — M_MT_MVCR3

32

+103C

MU MSI-X Table Message Address Register 4 — M_MT_MAR4

32

+1040

MU MSI-X Table Message Upper Address Register 4 — M_MT_MUAR4

32

+1044

MU MSI-X Table Message Data Register 4 — M_MT_MDR4

32

+1048

MU MSI-X Table Message Vector Control Register 4 — M_MT_MVCR4

32

+104C

MU MSI-X Table Message Address Register 5 — M_MT_MAR5

32

+1050

MU MSI-X Table Message Upper Address Register 5 — M_MT_MUAR5

32

+1054

MU MSI-X Table Message Data Register 5 — M_MT_MDR5

32

+1058

MU MSI-X Table Message Vector Control Register 5 — M_MT_MVCR5

32

+105C

MU MSI-X Table Message Address Register 6 — M_MT_MAR6

32

+1060

MU MSI-X Table Message Upper Address Register 6 — M_MT_MUAR6

32

+1064

MU MSI-X Table Message Data Register 6 — M_MT_MDR6

32

+1068

MU MSI-X Table Message Vector Control Register 6 — M_MT_MVCR6

32

+106C

MU MSI-X Table Message Address Register 7 — M_MT_MAR7

32

+1070

MU MSI-X Table Message Upper Address Register 7 — M_MT_MUAR7

32

+1074

MU MSI-X Table Message Data Register 7 — M_MT_MDR7

32

+1078

MU MSI-X Table Message Vector Control Register 7 — M_MT_MVCR7

32

+107C

Reserved

x

+1080 — +17FF

MU MSI-X Pending Bits Array Register

32

+1800

Reserved

x

+1804 — +1FFF

a. Relative to MU Base Address Offset.

Table 539. Messaging Unit (Sheet 2 of 2)

Register Description (Name)

Bits

Internal Bus Address Offset

a