41 pci configuration and status register - pcsr, 41pci configuration and status register - pcsr, 68 pci configuration and status register - pcsr – Intel CONTROLLERS 413808 User Manual

Page 178: Pci configuration and status register, Configuration and status register - pcsr, Intel, Bit default description, Hs_lstat, Hs_sm, Hs_freq[1: 0

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

178

Order Number: 317805-001US

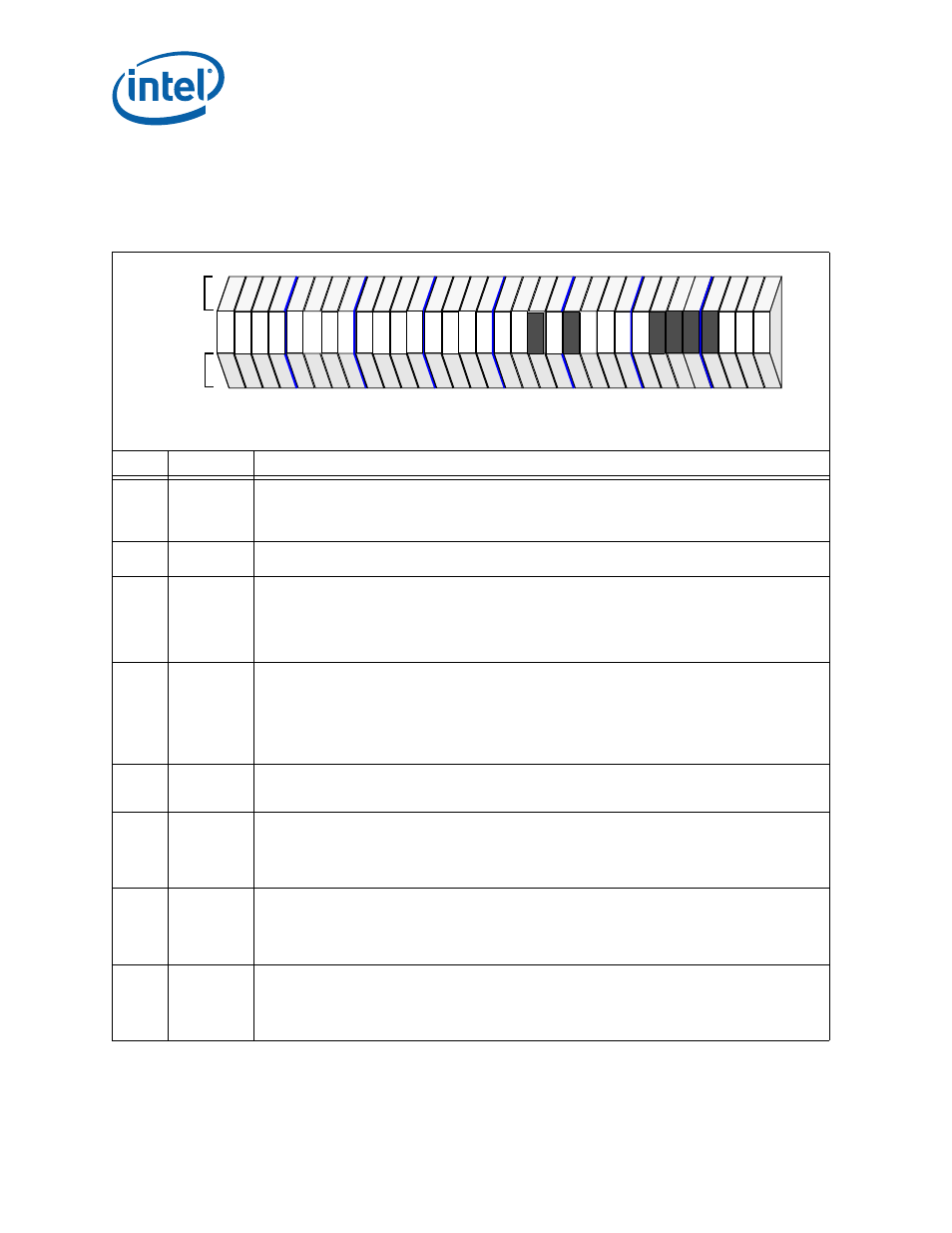

2.14.41 PCI Configuration and Status Register - PCSR

The PCI Configuration and Status Register has additional bits for controlling and

monitoring various features of the PCI bus interface.

Table 68. PCI Configuration and Status Register - PCSR (Sheet 1 of 3)

Bit

Default

Description

31:30

0

2

Initiate Core Processor Reset.

These bits are used to place the Intel XScale

®

processor processors into reset.

When a ‘1’ is written to this bits the corresponding Core Processor Reset (Bit 1:0)) is set.

This bit is self clearing and always reads ‘0’.

29

HS_LSTAT

Hot-Swap Latch Status:

Reflects the state of the HS_LSTAT pin.

28

HS_SM#

Hot-Swap Start up Mode:

Indicates 4138xx behavior when targeted by Configuration transactions with Configuration Retry Mode

enabled (bit 2 of the PCSR).

0 = 4138xx ignores all configuration transactions targeting it thereby causing the transaction to

ultimately Master Abort.

1 = 4138xx retries all configuration transactions targeting it.

27:26

HS_FREQ[1:

0]

Hot-Swap Frequency selection

These bits reflect the value on the HS_FREQ[1:0] pins when the

HS_SM#

strap is asserted.

11

PCI Mode, 33 or 66 MHz. Use P_M66EN to determine frequency

10

PCI-X Mode, 66 MHz

01

PCI-X Mode, 100 MHz

00

PCI-X Mode, 133 MHz

Note:

4138xx does not support CompactPCI Hot-Swap in PCI-X Mode2.

25

PCIX_EP#

PCIX End Point Strap

0 = ATUX is operating in End Point mode

1 = ATUX is operating as a central resource.

24

PCIXM1_10

0#

PCIX Mode1 - 100MHz limit

When all bus devices are capable of operating at greater then 66MHz, the

PCIXM1_100#

strap limits

the bus to operate at a maximum frequency of 100MHz.

0 = PCI-X Bus is limited to 100MHz operation in Mode 1

1 = PCI-X Bus can operate at 133MHz. in Mode 1

23

PCIXM2_10

0#

PCIX Mode2 - 100MHz limit (200MHz data rate)

When all bus devices are capable of operating at greater then 66MHz, the

PCIXM1_100#

strap limits

the bus to operate at a maximum frequency of 100MHz.

0 = PCI-X Bus is limited to 100MHz operation in Mode 1

1 = PCI-X Bus can operate at 133MHz. in Mode 1

22

EXTARB#

External Arbiter

When operating in Central Resource Mode (

PCIX_EP#

= 1), this strap enables the use of an external

arbiter

0 = External Arbiter Enabled

1 = External Arbiter Disabled (Use Internal Arbiter).

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

rw

rw

rw

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

rw

rw

rc

rc

rw

rw

rw

rw

rw

rw

rw

rw

ro

ro

ro

ro

rv

rv

rw

rw

rv

rv

ro

ro

ro

ro

ro

ro

rc

rc

rv

rv

rv

rv

rv

rv

rv

rv

rw

ro

co

co

co

co

Attribute Legend:

RV = Reserved

CO = Clear Only

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

+074H