Intel CONTROLLERS 413808 User Manual

Page 425

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

425

Messaging Unit—Intel

®

413808 and 413812

4.7.15

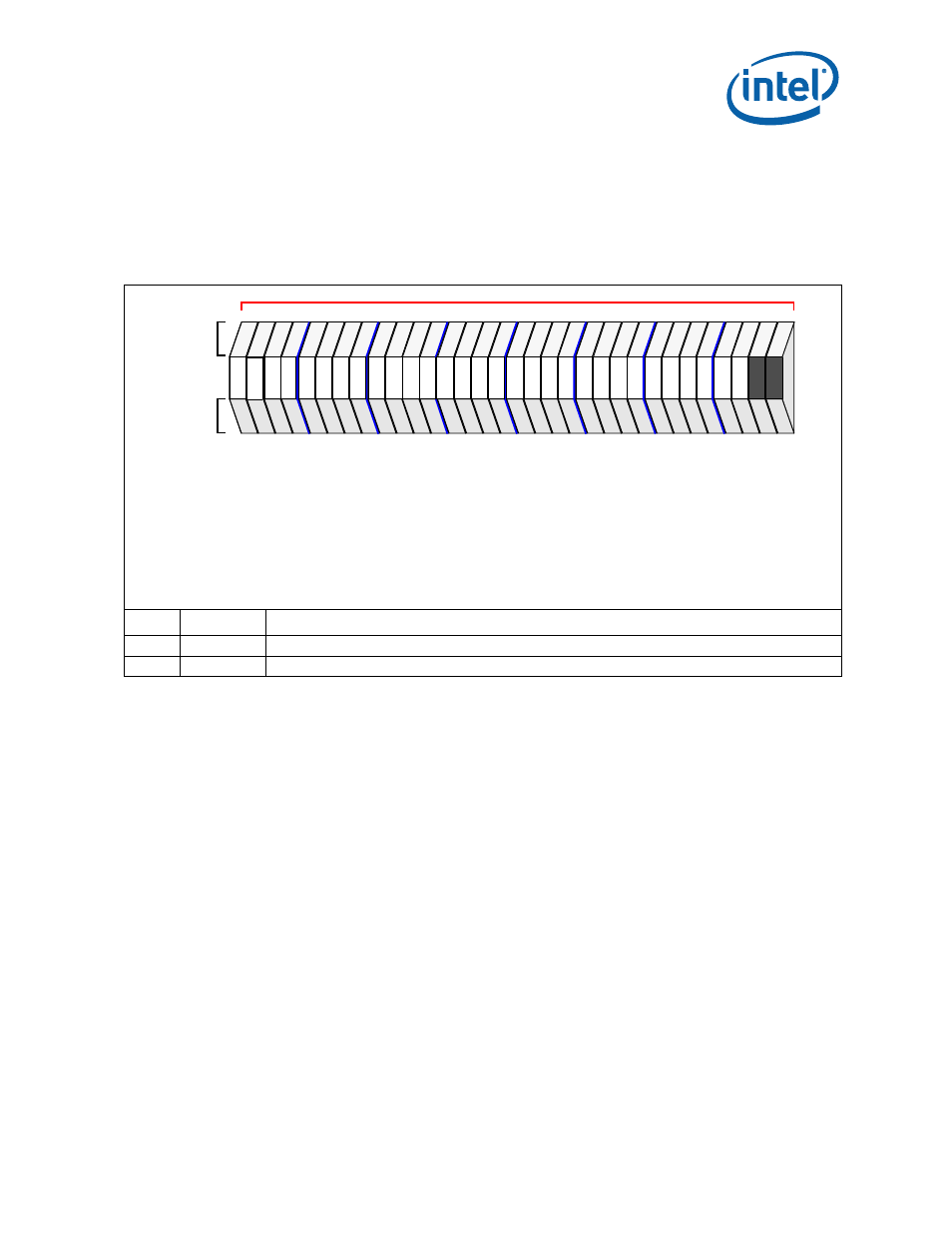

MU MSI-X Table Message Address Registers - M_MT_MAR[0:7]

The MU MSI-X Table Message Address Register contains the lower 30 bits of the MSI-X

message address. An entry in the MSI-X Table is made up of four DWORDs.

Note:

The M_MT_MAR[0:7] registers are not reset with an internal bus reset.

Table 280. MU MSI-X Table Message Address Registers - M_MT_MAR [0:7]

Bit

Default

Description

31:02 0000 0000H Message Lower Address: This field contains the lower 30 bits of the MSI-X Message Address.

01:00

00

2

Reserved.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rv rv

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rv rv

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

M_MT_MAR0

M_MT_MAR1

M_MT_MAR2

M_MT_MAR3

M_MT_MAR4

M_MT_MAR5

M_MT_MAR6

M_MT_MAR7

internal bus address

offset

5000H

5010H

5020H

5030H

5040H

5050H

5060H

5070H

M_MT_MAR0

M_MT_MAR1

M_MT_MAR2

M_MT_MAR3

M_MT_MAR4

M_MT_MAR5

M_MT_MAR6

M_MT_MAR7

MU/PCI Base Address

Offset

1000H

1010H

1020H

1030H

1040H

1050H

1060H

1070H