57 pci express capabilities register - pcie_cap, 57pci express capabilities register - pcie_cap, 197 pci express capabilities register pcie_cap – Intel CONTROLLERS 413808 User Manual

Page 342: Intel, Bit default description

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

342

Order Number: 317805-001US

3.17.57 PCI Express Capabilities Register - PCIE_CAP

This register controls various modes and features of ATU and Message Unit when

operating in the PCI Express mode.

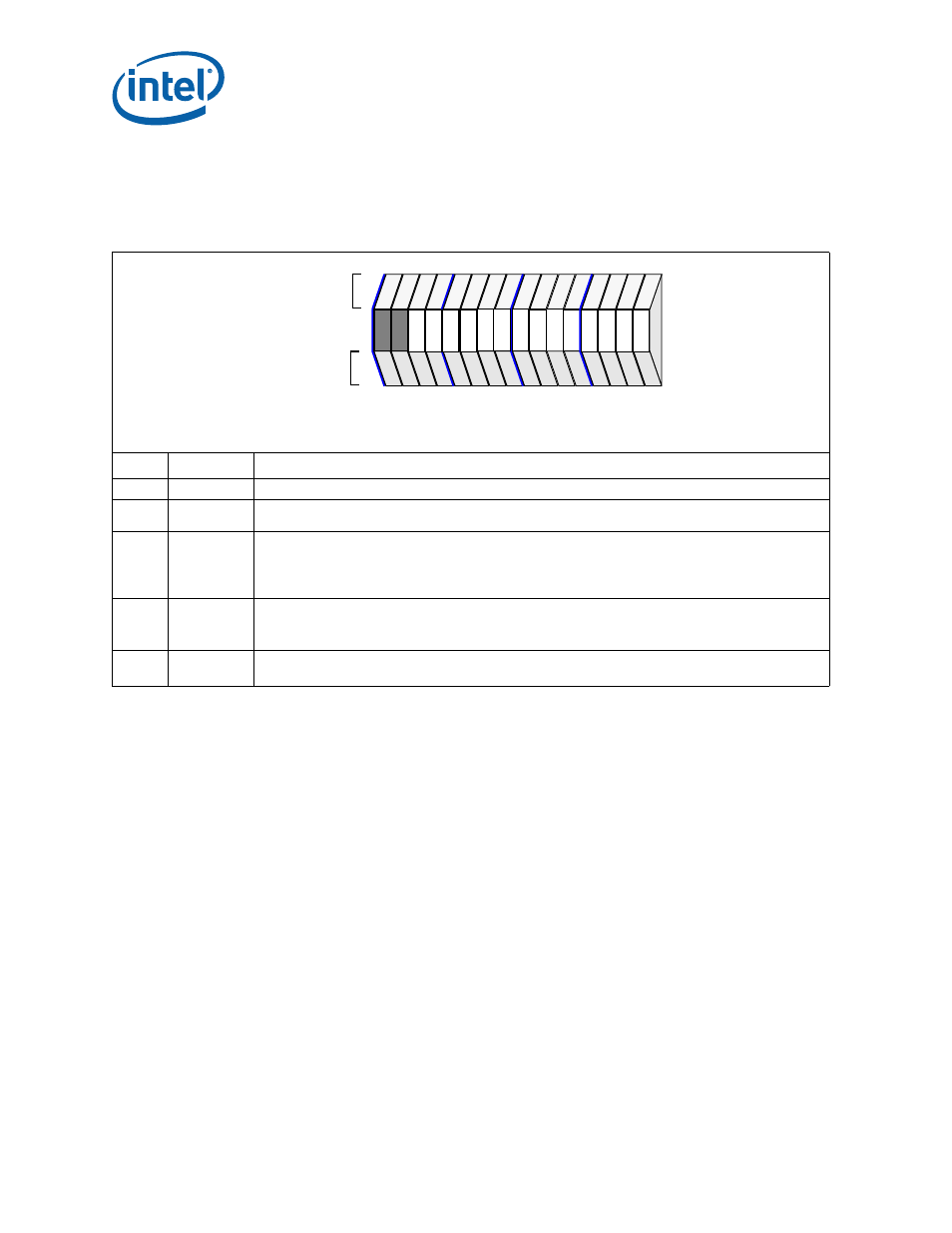

Table 197. PCI Express Capabilities Register PCIE_CAP

Bit

Default

Description

15:14

00

2

Preserved

13:9

00000

Interrupt Message Number - 4138xx uses a single interrupt message.

This register is hardcoded to 0.

8

Endpoint: 0

Root

Complex: 1

Slot Implemented - Indicates that the PCI Express Link associated with this port is connected to a slot.

Only valid for root complex and switch downstream ports.

Hard-wired to 0

Set to 1 for root complex this bit is initialized via strapping options.

7:4

0000

or

0100

Device/Port Type - Indicates the type of PCI Express logical device.

0000b - PCI Express Endpoint device

0100b - Root Port of PCI Express Root Complex these bits are initialized via strapping options.

3:0

1H

Capability Version - Indicates PCI-SIG defined PCI Express capability structure version number

4138xx supports version 1h.

PCI

IOP

Attributes

Attributes

15

12

8

4

0

pr

pr

pr

pr

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+0D2H