2 pmon event register 0-7 - pmon_evr[0:7, Table 493. pmon event register 0-7 - pmon_evr[0:7, Pmon – Intel CONTROLLERS 413808 User Manual

Page 753: Pmon unit—intel, Bit default description, Duration count, Occurrence count

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

753

PMON Unit—Intel

®

413808 and 413812

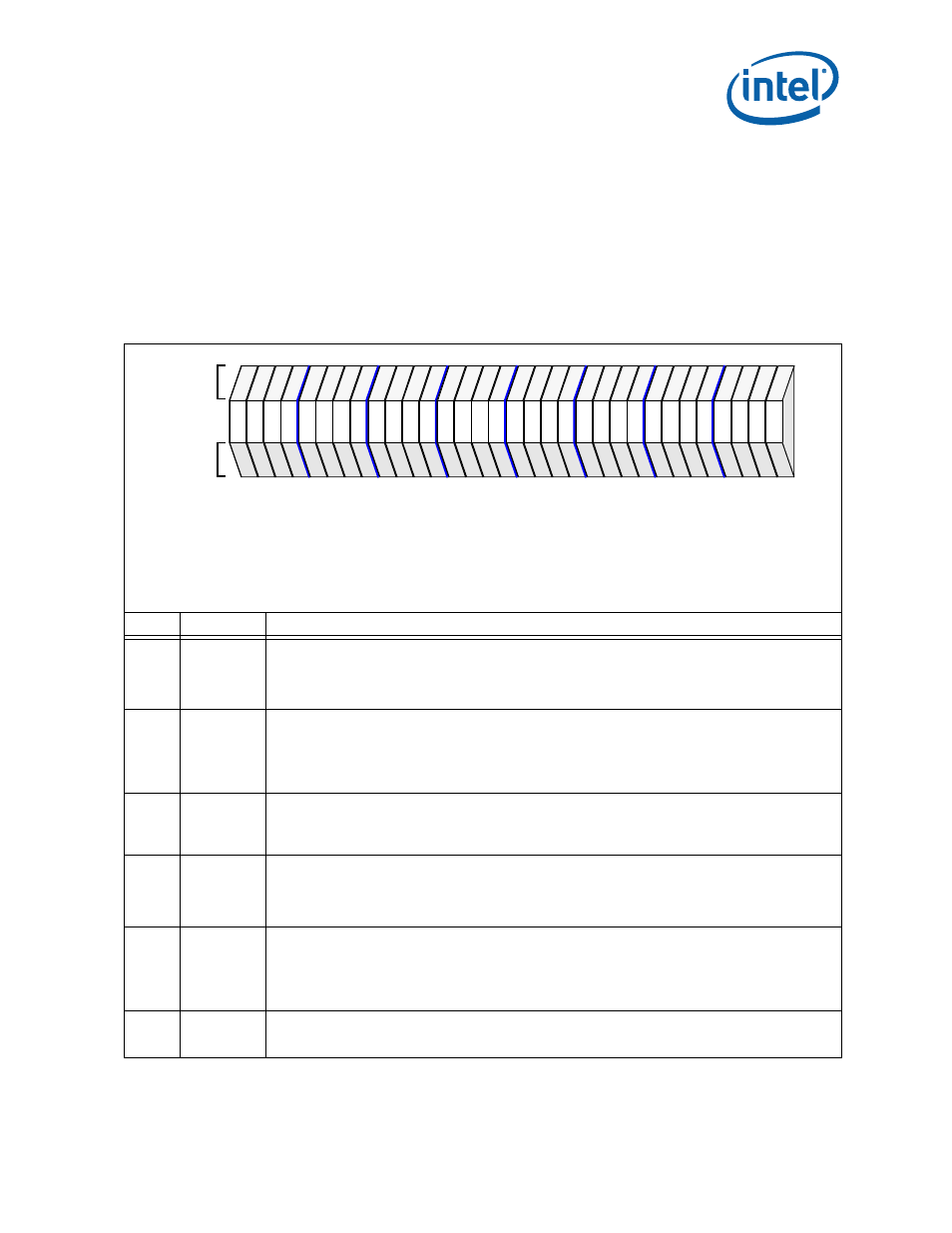

16.5.6.2 PMON Event Register 0-7 - PMON_EVR[0:7]

This 32-bit register contains the events that control the incrementing and

decrementing of the

PMON

counter selected. When this register is written, the

previous register contents are overwritten (the event fields are unbuffered) and the

associated counter is immediately affected by the change. This register should only be

programmed when the counter is idle and before the command register receives an

opcode that is associated with the events in this register. When both an increment and

a decrement event are detected on the same clock cycle, the counter value does not

change.

Table 493. PMON Event Register 0-7 - PMON_EVR[0:7]

Bit

Default

Description

31

0b

Decrement Occurrence Count Enable (DOCE)

0 = Decrement Duration Count: the counter is decremented for each clock for which the decrement

event signal is asserted logic high

1 = Decrement Occurrence Count: the counter is decremented each time a rising edge of the

decrement event signal is detected.

30:28

0h

Decrement Event Source Select (DESS)

This field expands the Event Selection Codes in the Decrement Event field to 1 of 8 ports, which share

the same codes. Normally driven to 000, unless another source of the same type is to be selected. For

4138xx, there are 8 different sources for SAS/SATA events, so setting these bits as “000” choose an

event from SAS/SATA Port-0, and setting these bits as “001” choose an event from SAS/SATA Port-1,

etc.

27:16

000h

Decrement Event (DE)

This field contains Event Selection Code (ESC) that the unit is required to detect before decrementing

the associated counter. This field is only applicable for opcodes putting the counter in a counting state.

Refer to the Event tables for valid values.

15

0b

Increment Occurrence Count Enable (IOCE)

0 = Increment

Duration Count

: the counter is incremented for each clock for which the increment

event signal is asserted logic high

1 = Increment

Occurrence Count

: the counter is incremented each time a rising edge of the

increment event signal is detected.

14:12

000b

Increment Event Source Select (IESS)

This field expands the Event Selection Codes in the Increment Event field to 1 of 8 ports, which share

the same codes. Normally driven to 000, unless another source of the same type is to be selected. For

4138xx, there are 8 different sources for SAS/SATA events, so setting these bits as “000” choose an

event from SAS/SATA Port-0, and setting these bits as “001” choose an event from SAS/SATA Port-1,

etc.

11:0

000h

Increment Event (IE)

This field contains the Event Selection Code (ESC) that the unit is required to detect before

incrementing the associated counter. Refer to the Event tables for valid values.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

PMON

_EVR0

PMON

_EVR1

PMON

_EVR2

PMON

_EVR3

PMON

_EVR4

PMON

_EVR5

PMON

_EVR6

PMON

_EVR7

+004h

+014h

+024h

+034h

+044h

+054h

+064h

+074h