32 inbound atu translate value register 1 - iatvr1, 32inbound atu translate value register 1 - iatvr1, 59 inbound atu translate value register 1 - iatvr1 – Intel CONTROLLERS 413808 User Manual

Page 172: Intel, Bit default description

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

172

Order Number: 317805-001US

2.14.32 Inbound ATU Translate Value Register 1 - IATVR1

The Inbound ATU Translate Value Register 1 (IATVR1) in conjunction with the

ATU Upper Translate Value Register 1 - IAUTVR1” on page 172

contain bits 35 to 12 of

the internal bus address used to convert PCI bus addresses. The converted address is

driven on the internal bus as a result of the Inbound ATU address translation.

2.14.33 Inbound ATU Upper Translate Value Register 1 - IAUTVR1

The Inbound ATU Upper Translate Value Register 1 (IAUTVR1) in conjunction with the

“Inbound ATU Translate Value Register 1 - IATVR1” on page 172

contain bits 35 to12 of

the internal bus address used to convert PCI bus addresses. The converted address is

driven on the internal bus as a result of the inbound ATU address translation.

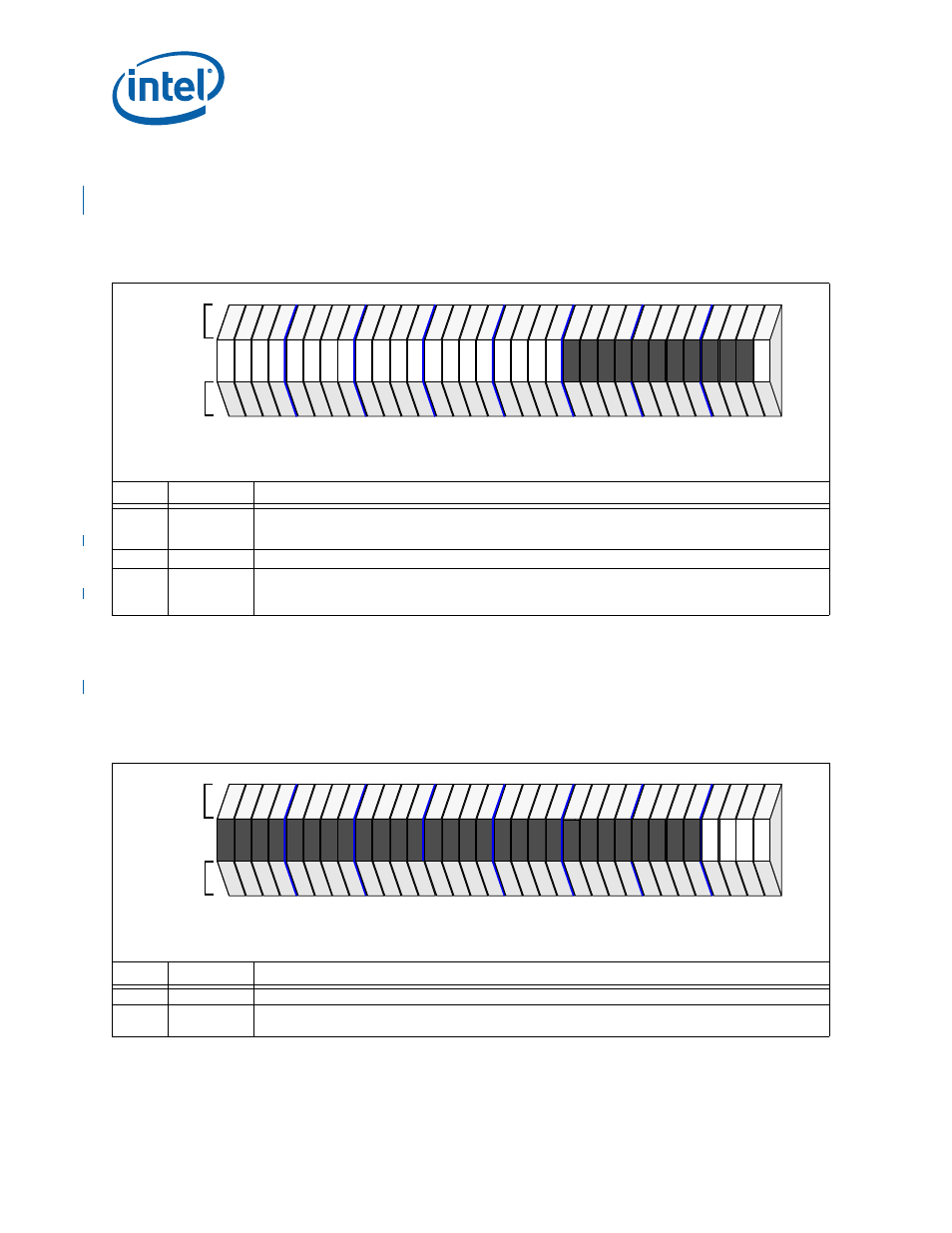

Table 59. Inbound ATU Translate Value Register 1 - IATVR1

Bit

Default

Description

31:12

00000H

Inbound ATU Translation Value 1: Bits 31 to 12 of the internal bus address used to convert the PCI

address to internal bus addresses. Must be naturally aligned with the IABAR1 register’s programmed

Section 2.14.23, “Determining Block Sizes for Base Address Registers” on page 164

).

11:01

000H

Reserved

00

0

Big Endian Byte Swap enable:

0 = No swap performed. See

Section 2.3, “Big Endian Byte Swapping” on page 78

for more details.

1 = Performs a byte swap on all PCI read/write transactions through BAR1.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

+050H

Table 60. Inbound ATU Upper Translate Value Register 1 - IAUTVR1

Bit

Default

Description

31:04

000 0000H Reserved

3:0

0H

Inbound Upper ATU Translation Value 1 - This value represents bits 35 to 32 of the internal bus address

used to convert the PCI address to internal bus addresses.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

rw

rw

rw

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

+054H