3 i2c slave address register x - isarx, Table 473. i2c slave address register x - isarx, 473 i – Intel CONTROLLERS 413808 User Manual

Page 719: C slave address register x — isarx, Table 473. i, The i, C bus interface units—intel, Bit default description, Slave address

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

719

I

2

C Bus Interface Units—Intel

®

413808 and 413812

14.8.3

I

2

C Slave Address Register x — ISARx

The I

2

C Slave Address Register (ISARx) (see

) defines the I

2

C unit 7-bit slave

address to which the 4138xx responds when in slave-receive mode. This register is

written by the 4138xx before enabling I

2

C operations. The register is fully

programmable (no address is assigned to the I

2

C unit) so it can be set to a value other

than those of hard-wired I

2

C slave peripherals that might exist in the system. The ISAR

is not affected by the 4138xx being reset. The ISAR register default value is 0000000

2

.

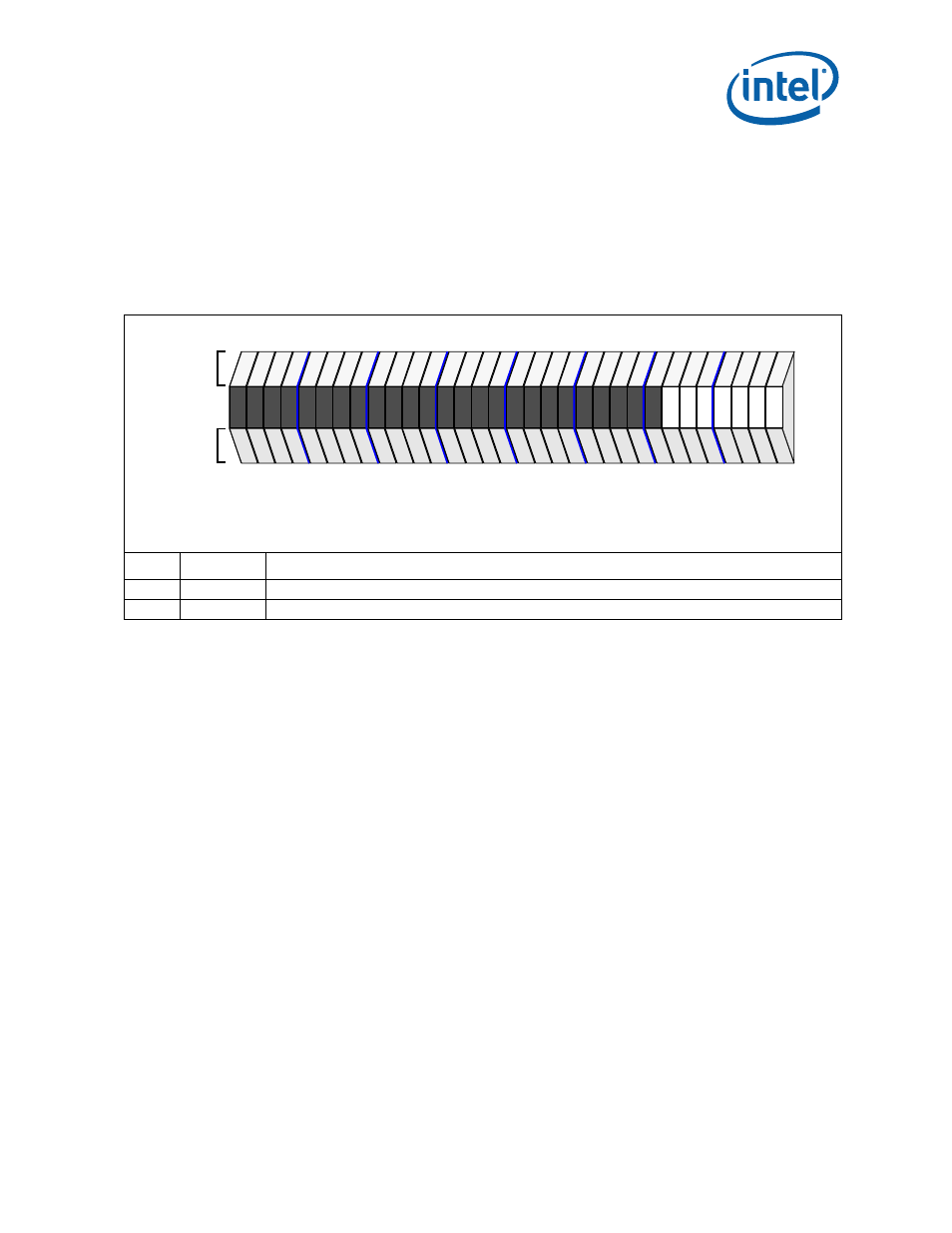

Table 473. I

2

C Slave Address Register x — ISARx

Bit

Default

Description

31:07

000000H Reserved

06:00

00H

I

2

C

Slave Address

: The 7-bit address to which the I

2

C unit responds when in slave-receive mode.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

Unit #

0

1

2

Intel XScale

®

processor internal bus address

offset

+2508H

+2528H

+2548H

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible