67 pci express root control register - pe_rcr, 67pci express root control register - pe_rcr, 207 pci express root control register - pe_rcr – Intel CONTROLLERS 413808 User Manual

Page 353: Pci express, Address translation unit (pci express)—intel, Bit default description

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

353

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

3.17.67 PCI Express Root Control Register - PE_RCR

This register controls PCI Express Slot specific parameters.

Table 207. PCI Express Root Control Register - PE_RCR

Bit

Default

Description

15:4

0H

Reserved

3

0

PME Interrupt Enable

This bit when set enables interrupt generation upon receipt of a PME message as reflected in the PME

Status register bit. A PME Interrupt is also generated when the PME Status register bit is set when this

bit is set from a cleared state.

2

0

System Error on Fatal Error Enable

When set, the ATU generates the ATU_SERR interrupt when a fatal error (ERR_FATAL) message is

received or a fatal error is detected by ATU. This is only valid when operating as the root complex

1

0

System Error on Non-Fatal Error Enable

When set, the ATU generates the ATU_SERR interrupt when a non-fatal error (ERR_NONFATAL) message

is received or a non-fatal error is detected by ATU. This is only valid when operating as the root complex

0

0

System Error on Correctable Error Enable

When set, the ATU generates the ATU_SERR interrupt when a correctable error (ERR_COR) message is

received or a correctable error is detected by ATU. This is only valid when operating as the root complex

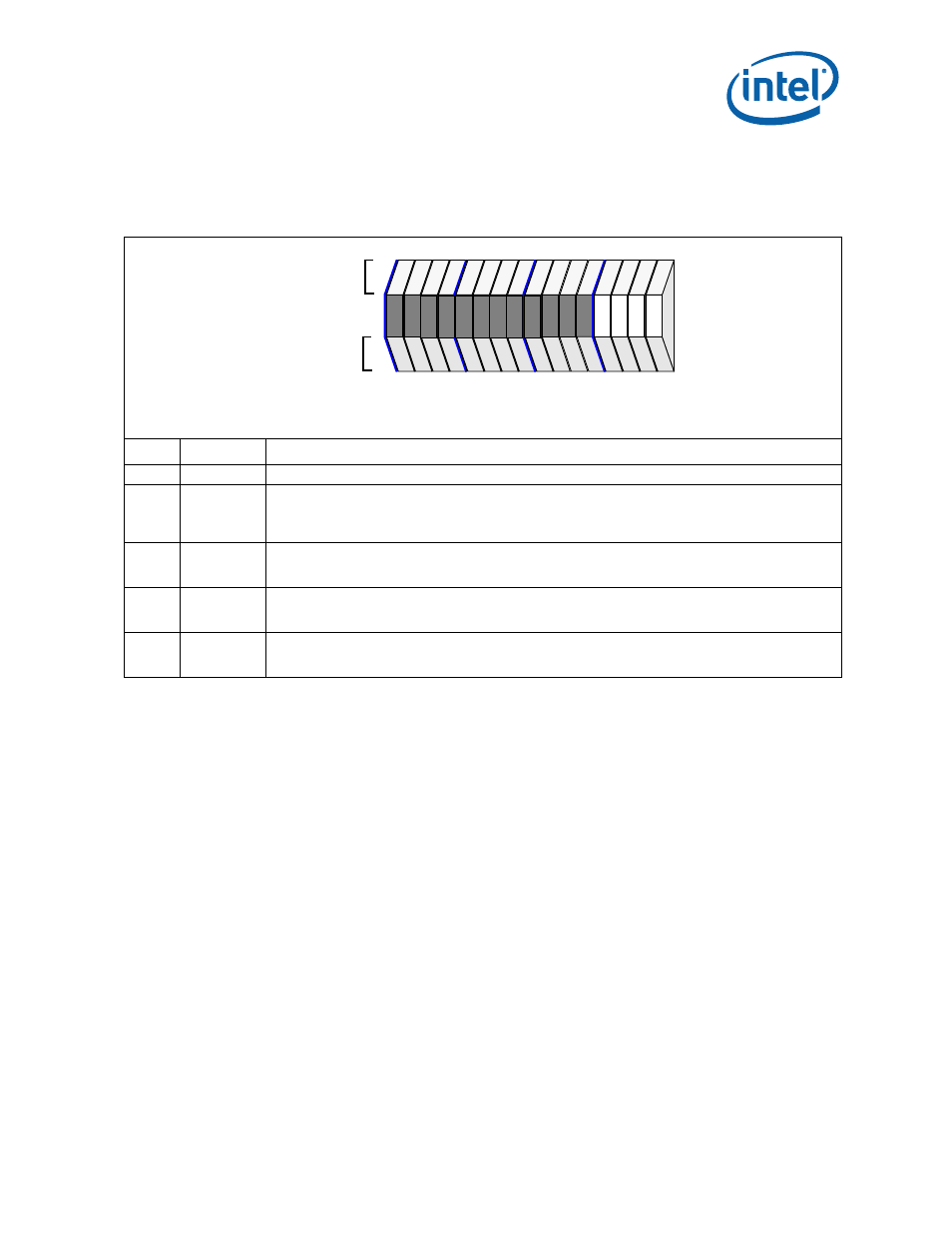

PCI

IOP

Attributes

Attributes

15

12

8

4

0

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+0ECH