3 configuration and memory writes – Intel CONTROLLERS 413808 User Manual

Page 652

Intel

®

413808 and 413812—SMBus Interface Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

652

Order Number: 317805-001US

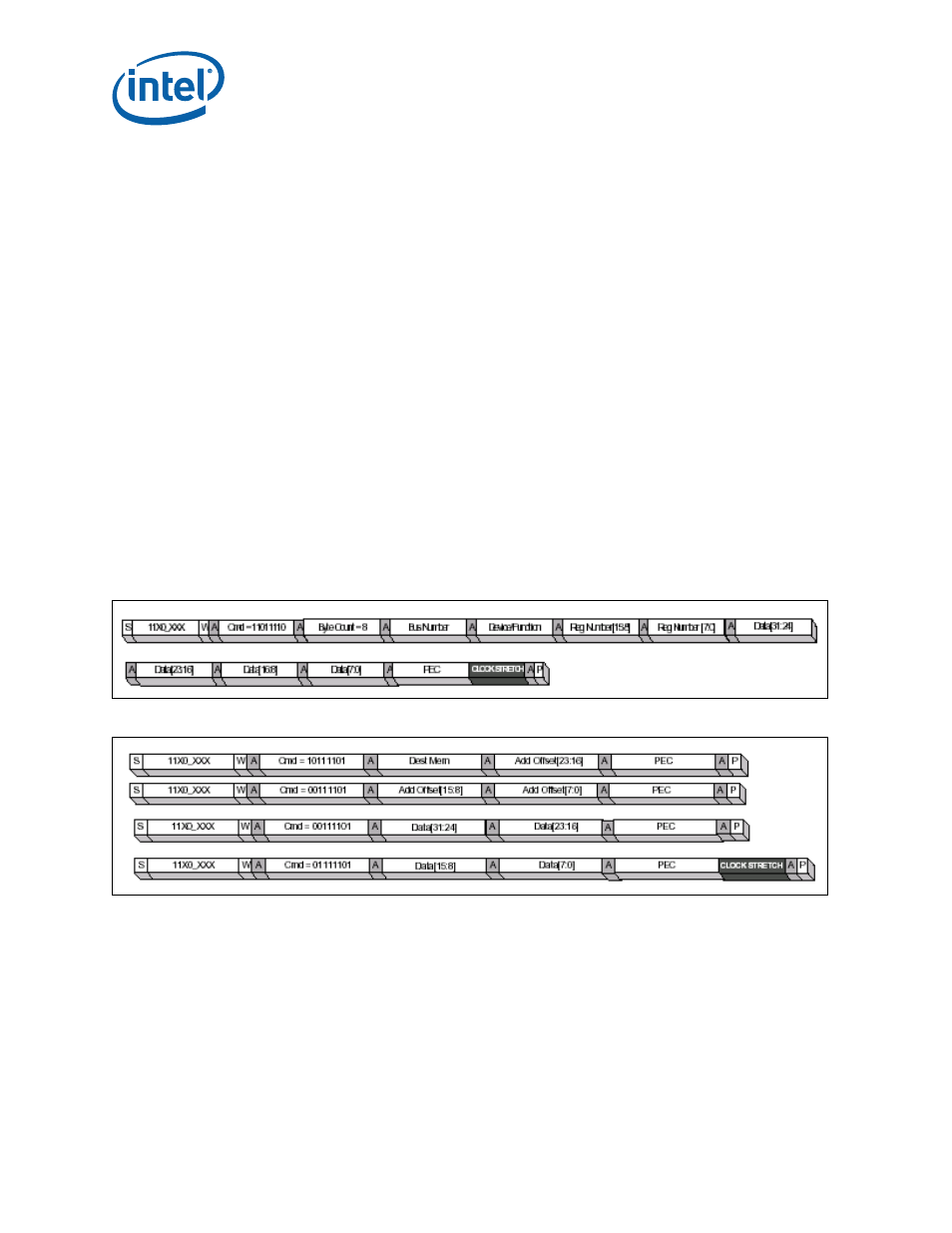

12.3.3.3 Configuration and Memory Writes

Configuration and memory writes are accomplished through a series of SMBus writes.

As with reads, a write sequence is first used to initialize the Bus Number, Device,

Function, and Register Number for the configuration access and the destination

memory, address offset for the memory write. The writing of this information can be

accomplished through any combination of the supported SMBus write commands

(Block, Word or Byte).

Note: On SMBus, there is no concept of byte enables. Therefore, the Register Number

written to the slave is assumed to be aligned to the length of the Internal Command. In

other words, for a Write Byte internal command, the Register Number specifies the

byte address. For a Write DWord internal command, the two least-significant bits of the

Register Number are ignored. This is different from PCI where the byte enables are

used to indicate the byte of interest.

After all the information is set up, the SMBus master initiates one or more writes which

sets up the data to be written. The final write (End bit is set) initiates an internal

configuration or memory write. The slave interface could potentially clock stretch the

last data write until the write completes without error. When an error occurred, the

SMBus interface NACKs the last write operation just before the stop bit. Examples of

configuration writes are illustrated below. All the figures are with PEC Enabled. When

PEC is disabled, there is no PEC byte in any of the sequences and the PEC enable bit in

the command field is 0.

For the definition of the diagram conventions below, refer to the System Management

Bus Specification, Revision 2.0.

Figure 86. DWORD Configuration Write Protocol (SMBus Block Write, PEC Enabled)

Figure 87. DWORD Memory Write Protocol (SMBus Word Write, PEC Enabled)