2 error interrupt sources, Table 380. error interrupt sources, 380 error interrupt sources – Intel CONTROLLERS 413808 User Manual

Page 578

Intel

®

413808 and 413812—Interrupt Controller Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

578

Order Number: 317805-001US

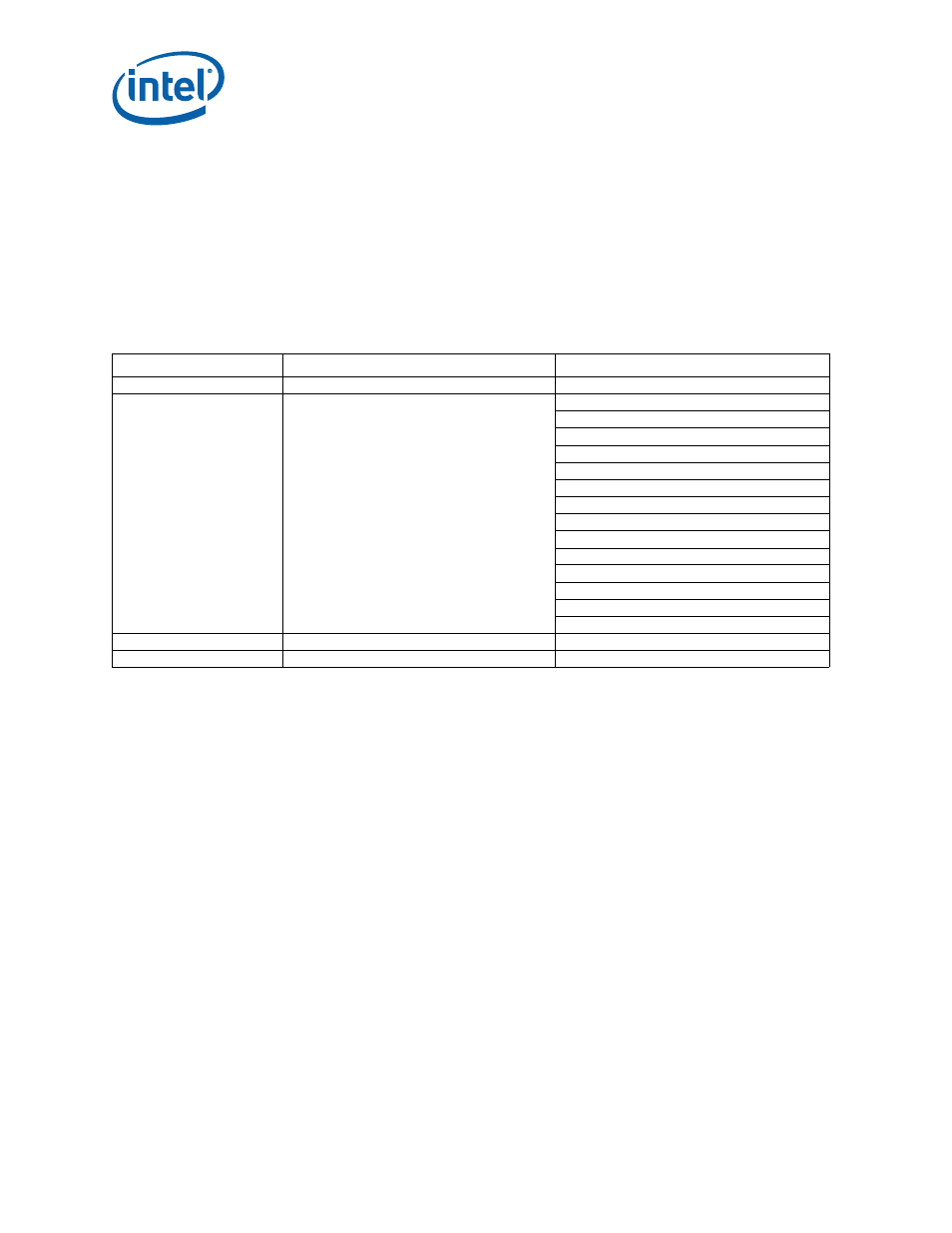

10.5.3.2 Error Interrupt Sources

The 4138xx Interrupt Controller receives error interrupts from the ATUs, the Messaging

Unit. Each of these interrupts represent an error condition in the peripheral unit. Refer

to the appropriate units for more details.

A valid interrupt from any of these sources, outputs a level-sensitive interrupt to the

4138xx Interrupt Controller input. The corresponding FIQ or IRQ interrupt source

register bit in the interrupt controller remains active as long as the interrupt is pending

in the peripheral unit. The appropriate FIQ or IRQ interrupt source bit is cleared by

clearing the source of the interrupt at the internal peripheral.

Table 380. Error Interrupt Sources

Unit

Register

Error Condition

Intel XScale

®

processor

L2 Cache/BIU Error Logging Register (ERRLOG) L2 cache single bit ECC error.

ATU -X & -E

ATU -X & -E Interrupt Status Register

ATU Vital Product Data Address Updated

ATU Inbound Memory Window 1 Base Updated

Initiated Split Completion Error Message

Received Split Completion Error Message

Power State Transition

P_SERR#

Asserted

PCI Detected Parity Error

ATU BIST Interrupt

IB Master Abort

P_SERR#

Detected

PCI Master Abort

PCI Target Abort (master)

PCI Target Abort (target)

PCI Master Parity Error

Messaging Unit

Inbound Interrupt Status Register

Error Doorbell Interrupt

Watch Dog Time

Timer Interrupt Status Register

Timer Expiration