86 internal arbiter control register - iacr, 86internal arbiter control register - iacr, 113 internal arbiter control register - iacr – Intel CONTROLLERS 413808 User Manual

Page 224: Intel, Bit default description

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

224

Order Number: 317805-001US

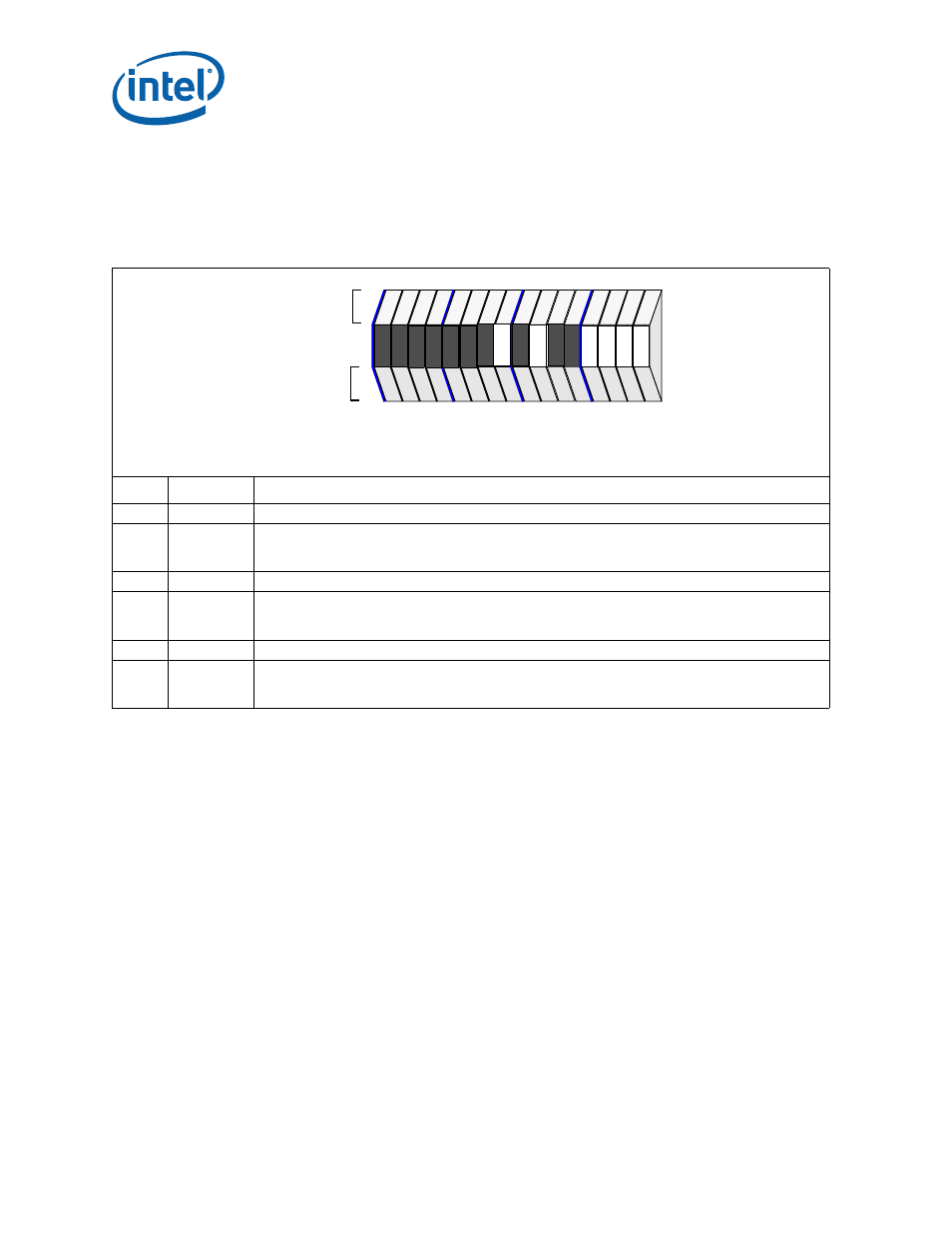

2.14.86 Internal Arbiter Control Register - IACR

The Internal Arbiter Control Register is used to control which priority ring different PCI

bus requesters (including the ATU) use. In addition, the method by which the arbiter

parks on masters is configurable in this register.

Table 113. Internal Arbiter Control Register - IACR

Bit

Default

Description

15:9

0

2

Reserved.

08

0

2

Bus Parking Control: Controls the bus parking behavior of the internal arbiter:

0 = Bus is parked on the last PCI agent using the bus.

1 = Bus is always parked on 4138xx.

07

0

2

Reserved

06

0

2

ATU Ring Allocation: Priority ring allocation for 4138xx ATU requests:

0 = The ATU is in the low priority ring of the internal arbiter.

1 = The ATU is in the high priority ring of the internal arbiter.

05:04:

00

2

Reserved.

03:00

0000

2

PCI Master Priority Ring Allocation: Bit 0 corresponds to REQ#[0], 1 corresponds to REQ#[1] and so on:

0 = The corresponding master is in the low priority ring of the internal arbiter.

1 = The corresponding master is in the high priority ring of the internal arbiter.

PCI

IOP

Attributes

Attributes

15

12

8

4

0

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

ro

rv

rv

rw

ro

rv

rv

rv

rv

rw

ro

rw

ro

rw

ro

rw

ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

+394H