2 outbound address translation windows – Intel CONTROLLERS 413808 User Manual

Page 246

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

246

Order Number: 317805-001US

3.3.2.2

Outbound Address Translation Windows

Inbound translation involves a programmable inbound translation window consisting of

a base and limit register and a value register for PCI to internal bus translation. The

outbound address translation windows use a similar methodology except that the

outbound translation window limit sizes are fixed in 4138xx internal bus address space;

this removes the need for separate limit registers.

illustrates the five outbound address translation windows. The

ATU has four 4 Gbyte outbound memory translation windows and one 64 Kbyte

outbound I/O translation window. By default, Outbound Memory Window 0

(OUMBAR0), Outbound Memory Window 1 (OUMBAR1), Outbound Memory Window 2

(OUMBAR2), and the Outbound Memory Window 3 (OUMBAR3) reside in 4 Gbyte

memory sections 1, 2, 3, and 4, respectively. The default location of the 64 KByte

outbound I/O window range is from 0.FFFD.0000H to 0.FFFD.FFFFH. The following

registers are used to specify the five 4 Gbyte windows for claiming Outbound Memory

transactions:

• Outbound Upper Memory Base Address Register 0 (OUMBAR0)

— Default Value equal to 01H.

• Outbound Upper Memory Base Address Register 1 (OUMBAR1)

— Default Value equal to 02H.

• Outbound Upper Memory Base Address Register 2 (OUMBAR2)

— Default Value equal to 03H.

• Outbound Upper Memory Base Address Register 3 (OUMBAR3)

— Default Value equal to 04H.

• Outbound I/O Base Address Register (OIOBAR)

— Default Value equal to 0FFF D000H

An internal bus cycle with an address within one of the outbound windows initiates a

read or write request on the PCI Express Link. The PCI transaction type depends on

which translation window the local bus cycle “hits”. The read or write decision is based

on the internal bus cycle type.

ATU has windows dedicated to the following outbound transaction types:

• Memory reads and Memory writes - Memory Window

• I/O reads and writes - I/O Window

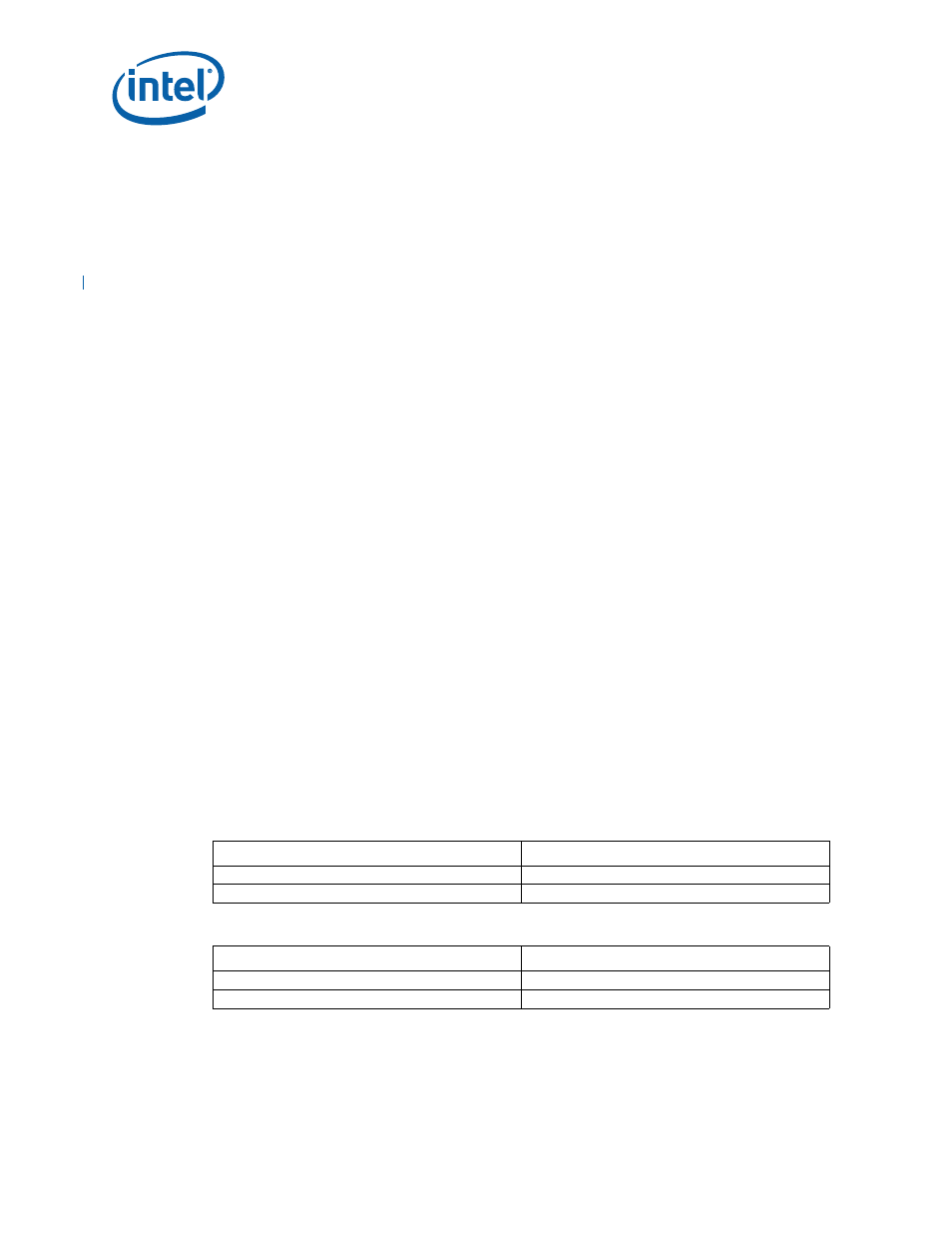

Table 123. Internal Bus-to-PCI Command Translation for Memory Windows

Internal Bus Command

PCI Express Transaction Type

Write

Memory Write Request

Read

Memory Read Request

Table 124. Internal Bus-to-PCI Command Translation for I/O Window

Internal Bus Command

a

a. User should designate memory region containing I/O Window as non-cachable and non-bufferable from Intel

XScale

®

processor. This insures all load/stores to I/O Window are of DWORD quantities. In the event that the

user inadvertently issues a read to the I/O Window which crosses a DWORD address boundary, the ATU target

aborts the transaction. Only bytes 3:0 is relevant dependent on the Byte Enables.

Conventional PCI Command

Write

I/O Write Request

Read

I/O Read Request