8 bridge window limit register - bwlr, Table 341. bridge limit register - bwlr, 8 bridge window limit register — bwlr – Intel CONTROLLERS 413808 User Manual

Page 507: 341 bridge limit register — bwlr, Bridge limit register — bwlr, Table 341. bridge limit register — bwlr, Bit default description, Intel, 12 fff0 0h, Processor local bus address

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

507

System Controller (SC) and Internal Bus Bridge—Intel

®

413808 and 413812

7.5.8

Bridge Window Limit Register — BWLR

The 4138xx limit register’s (BWLR) programmed value must be naturally aligned with

the base address register’s (BWBAR) programmed value. The limit register is used as a

mask when the address decode for Bridge memory window is performed.

.

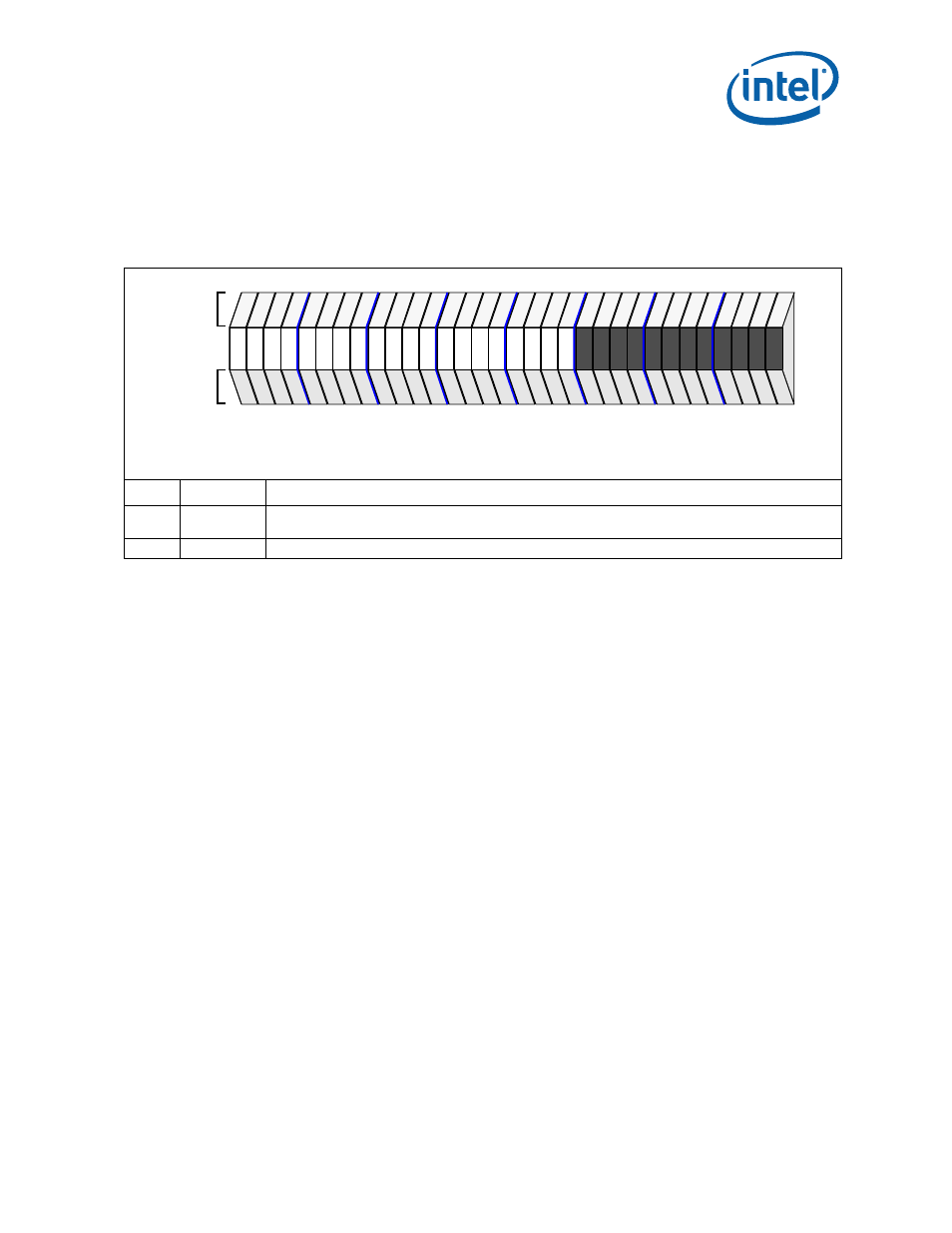

Table 341. Bridge Limit Register — BWLR

Bit

Default

Description

31:12

FFF0 0H

Bridge Memory Window Limit:

This value determines the memory range required for the Bridge

Memory Window. Defaults to a 1MB Memory Window.

11:00

000H

Reserved

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Intel XScale

®

processor Local Bus Address

Offset

+1788H

South XBG