1 data transfer examples, 2 configuration and memory reads, Table 432. smbus status byte encoding – Intel CONTROLLERS 413808 User Manual

Page 649: 432 smbus status byte encoding

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

649

SMBus Interface Unit—Intel

®

413808 and 413812

12.3.3.1 Data Transfer Examples

, the following terminology is used:

S

Start Bit

Sr

Start Repeat Bit

W

Write Command

R

Read Command

A

Acknowledge

N

Retry / not Acknowledge

P

Stop Bit

Clear boxes indicate phases of the cycle driven by the initiator, and shaded boxes

indicate phases of the cycle driven by the target.

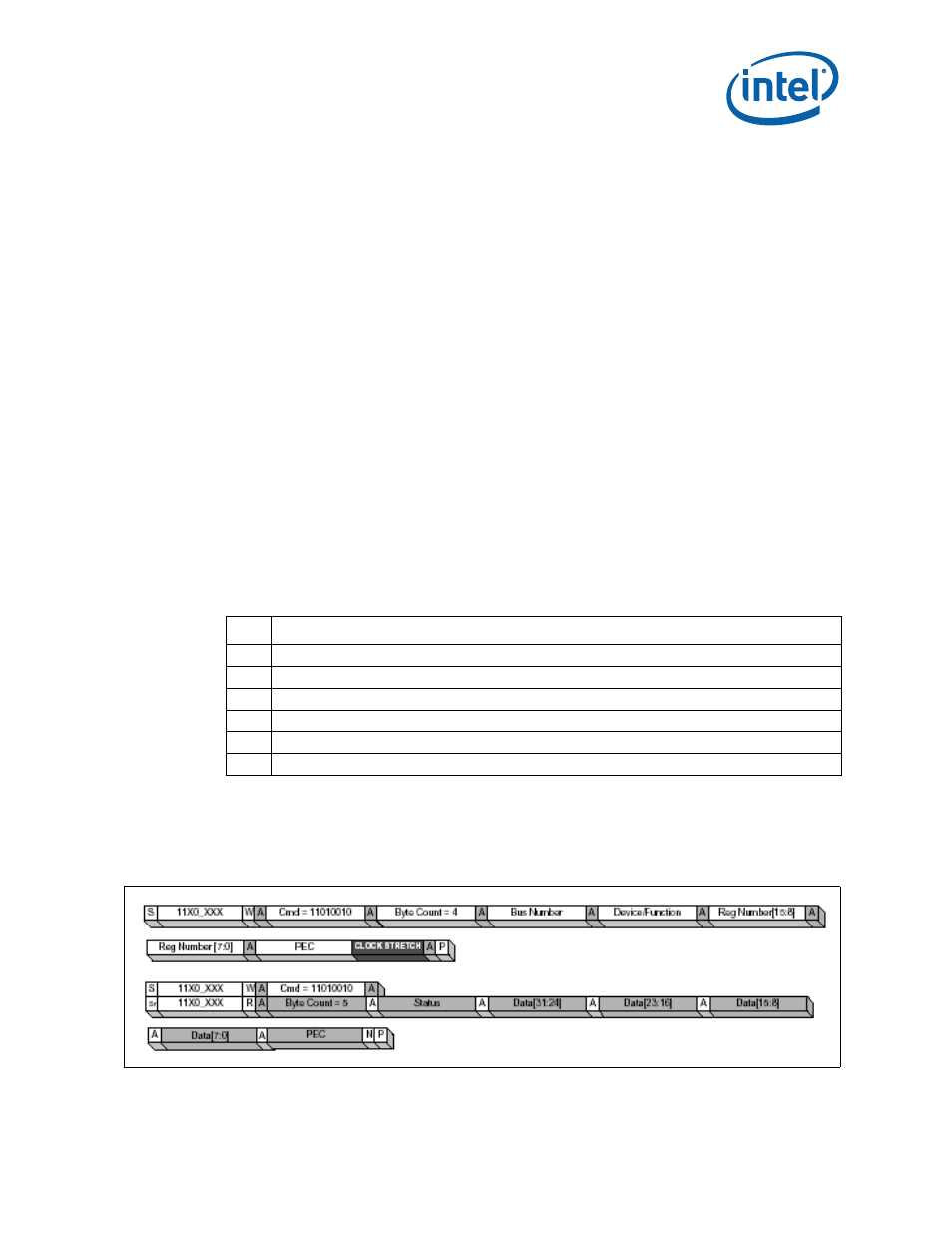

12.3.3.2 Configuration and Memory Reads

4138xx supports only read dword to internal register space. All Configuration and

memory reads are accomplished through an SMBus write(s) and later followed by an

SMBus read to read the status and the read data. For SMBus read transactions, the last

byte of data (or the PEC byte when enabled), is NACKed by the master to indicate the

end of the transaction. The SMBus memory read command returns the status of the

previous internal command and the data associated previous internal read command.

The status field encoding is:

Examples of configuration and memory reads are shown in

through

. For the definition of the diagram conventions below, refer to the System

Management Bus Specification, Revision 2.0.

Table 432. SMBus Status Byte Encoding

Bit

Description

7

Reserved

6

Internal Address Error

5

Internal Master Abort

4

Internal Target Abort

3:1 Reserved

0

Successful

Figure 78. DWORD Configuration Read Protocol (SMBus Block Write/Block Read, PEC

Enabled)