Intel CONTROLLERS 413808 User Manual

Page 123

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

123

Address Translation Unit (PCI-X)—Intel

®

413808 and 413812

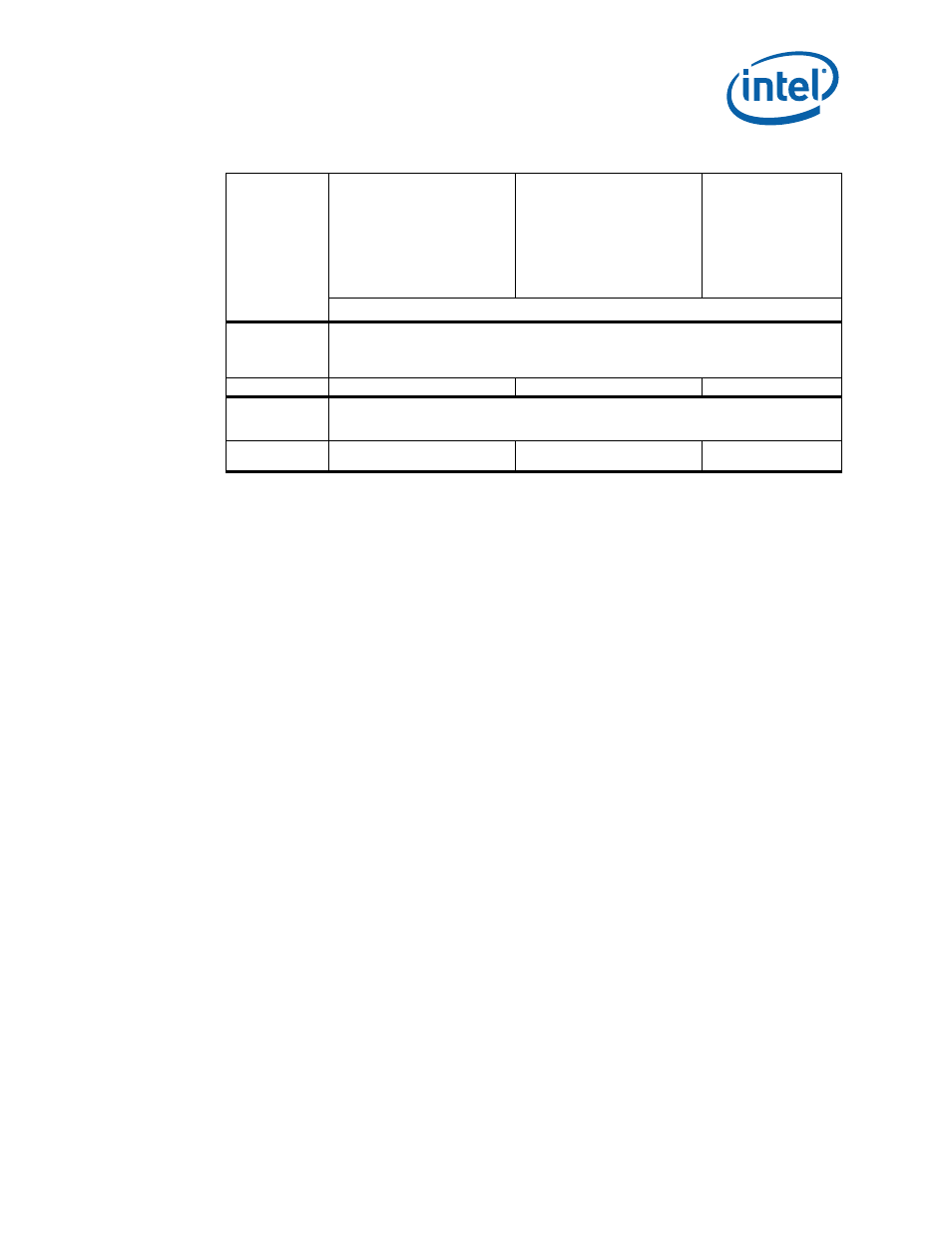

Inbound EROM

Write Request

Target-Abort

(All)

Signal Target-Abort.

(All)

Target Abort (target) - bit 11

PCI Target Abort (target) - bit 1 ATUIMR bit 3

Unexpected Split

Completion

(PCI-X)

In the PCI-X mode, the transaction completes normally according to the invalid lower

address field or invalid byte count.

(PCI-X)

Unexpected Split Completion -

bit 19

N/A

N/A

a. Codes for bus mode in which this error response applies: PCI-X means PCI-X Mode 1 or PCI-X Mode 2, PCI-X2

means PCI-X Mode 2 only, Conventional means Conventional PCI Mode Only, and All means that the error

response applies in the Conventional, PCI-X Mode 1 and PCI-X Mode 2 modes of operation. MSI stands for

Message-Signaled Interrupts and refers to an Outbound Write transaction that is actually an MSI write

transaction.

b. Table assumes that Parity Error Response - bit 6 of the ATUCMD register is set.

c. Table assumes that Data Parity Recovery Enable - bit 0 of the PCIXCMD is clear.

d. When a correctable or uncorrectable data error occurs in PCI-X Mode 2, the ECC Logging registers consisting

of the

ECC Control and Status Register - ECCCSR

, the

ECC First Address Register - ECCFAR

, the

, and the

ECC Attribute Register - ECCAR

are updated with additional information

about the ECC error.

e. When the SCE bit (bit 30 of the Completer Attributes) and the SCM bit (bit 29 of the Completer Attributes) are

set during the Attribute phase of a Split Completion Transaction, the transaction is a Split Completion Message

that is an Error Message. In this case, the Received Split Completion Error Message - bit 29 of the PCIXSR is

set.

Table 18. ATU Error Reporting Summary - PCI Interface (Sheet 5 of 5)

Error Condition

(Bus Mode

a

)

Bits Set in

ATU Status Register

(ATUSR

b

)

or

PCI-X Status Register

(PCIXSR

c

)

and/or

ECC Logging Registers

d

(ECCLOG)

Bits Set in

ATU Interrupt Status

Register (ATUISR)

Interrupt Mask Bit in

ATUIMR or ATUCR

PCI Bus Error Response (i.e., signal Target-Abort, signal Master-Abort etc.)