Table 120. atu command support, 120 atu command support – Intel CONTROLLERS 413808 User Manual

Page 236

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

236

Order Number: 317805-001US

Inbound and outbound ATU transactions are best described by the data flows used on

the PCI Express Link and the 4138xx internal bus during read and write operations. The

following sections describe read and write operations for inbound ATU transactions (PCI

Express to internal bus) and outbound transactions (internal bus to PCI Express). All

transactions are full split and the requests and completions are described separately.

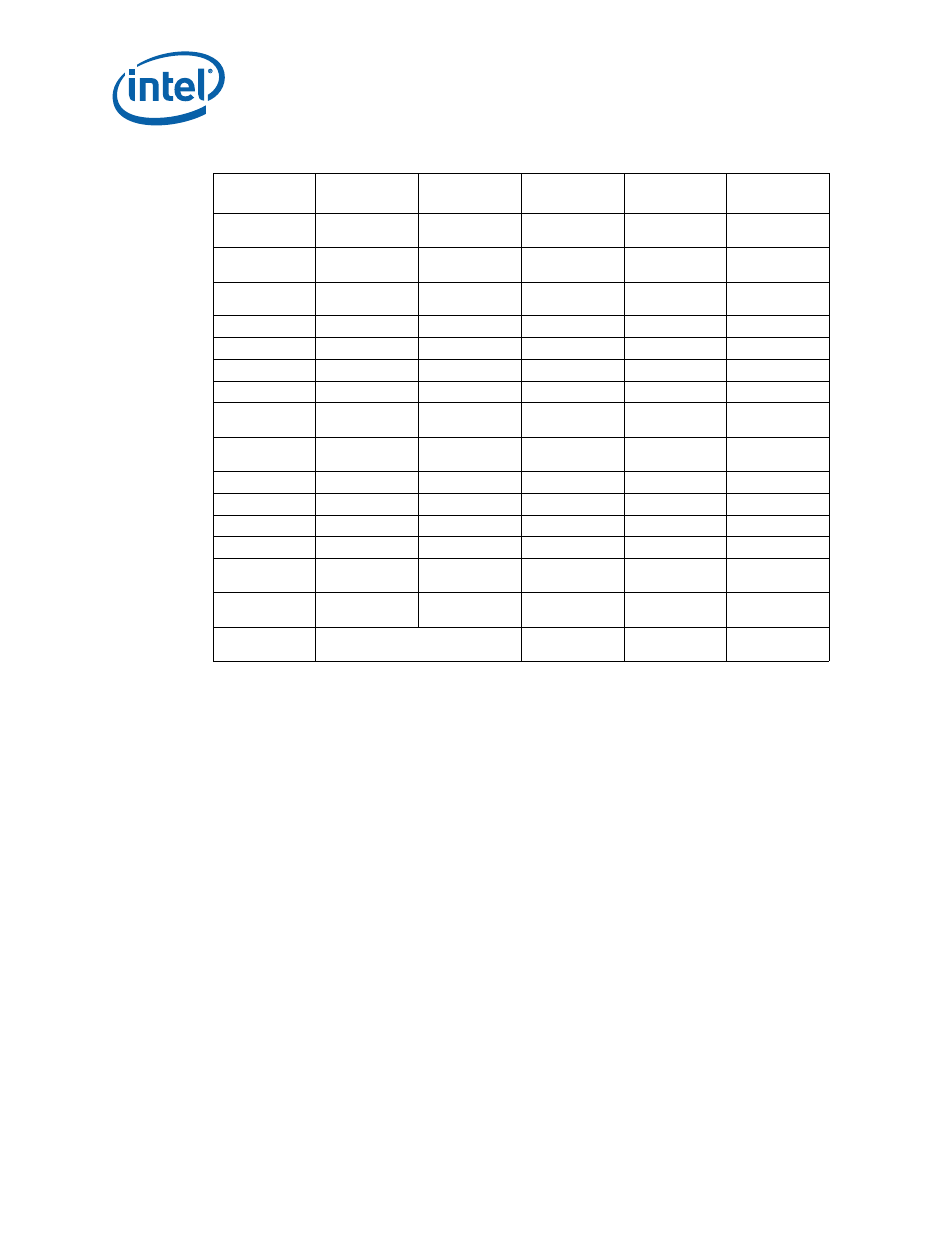

Table 120. ATU Command Support

TLP Type

Fmt[1:0]

a

Type[4:0]

Supported as

Completer

Generated as

Requester

Valid Internal

Bus Command

MRd

00

01

0 0000

Yes

Yes

Read

MRdLk

00

01

0 0001

Unsupported

Request

No

N/A

MWr

10

11

0 0000

Yes

Yes

Write

IORd

00

0 0010

Yes

Yes

Read

IOWr

10

0 0010

Yes

Yes

Write

CfgRd0

00

0 0100

Yes

Yes

Read

CfgWr0

10

0 0100

Yes

Yes

Write

CfgRd1

00

0 0101

Unsupported

Request

Yes

N/A

CfgWr1

10

0 0101

Unsupported

Request

Yes

N/A

Msg

01

1 0r

2

r

1

r

0

Yes

Yes

Write

b

MsgD

11

1 0r

2

r

1

r

0

Yes

Yes

Write

Cpl

00

0 1010

Yes

Yes

Completion

CplD

10

0 1010

Yes

Yes

Completion

CplLk

00

0 1011

Unexpected

Completion

c

No

N/A

CplDLk

10

0 1011

Unexpected

Completion

No

N/A

All encodings not shown above are

reserved

Malformed

Packet

No

N/A

a. Requests with two Fmt[1:0] values shown can use either 32b (the first value) or 64b (the second value)

Addressing Packet formats.

b. As a completer, the ATU stores the message header and payload directly in memory mapped registers. No

internal bus traffic occurs.

c. ATU does not generate lock requests and any CplLk or CplDLk would be an unexpected completion.