Table 352. sram ecc control register - secr, 352 sram ecc control register — secr, Table 352. sram ecc control register — secr – Intel CONTROLLERS 413808 User Manual

Page 537: Bit default description, Single bit error correction enable, Multi-bit error reporting enable, Single bit error reporting enable

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

537

SRAM Memory Controller—Intel

®

413808 and 413812

• Disable single-bit error reporting

• Enable single-bit error correcting

For more details, see

Section 8.3.3, “Error Correction and Detection” on page 519

and

Section 8.4, “ECC Interrupts/Error Conditions” on page 531

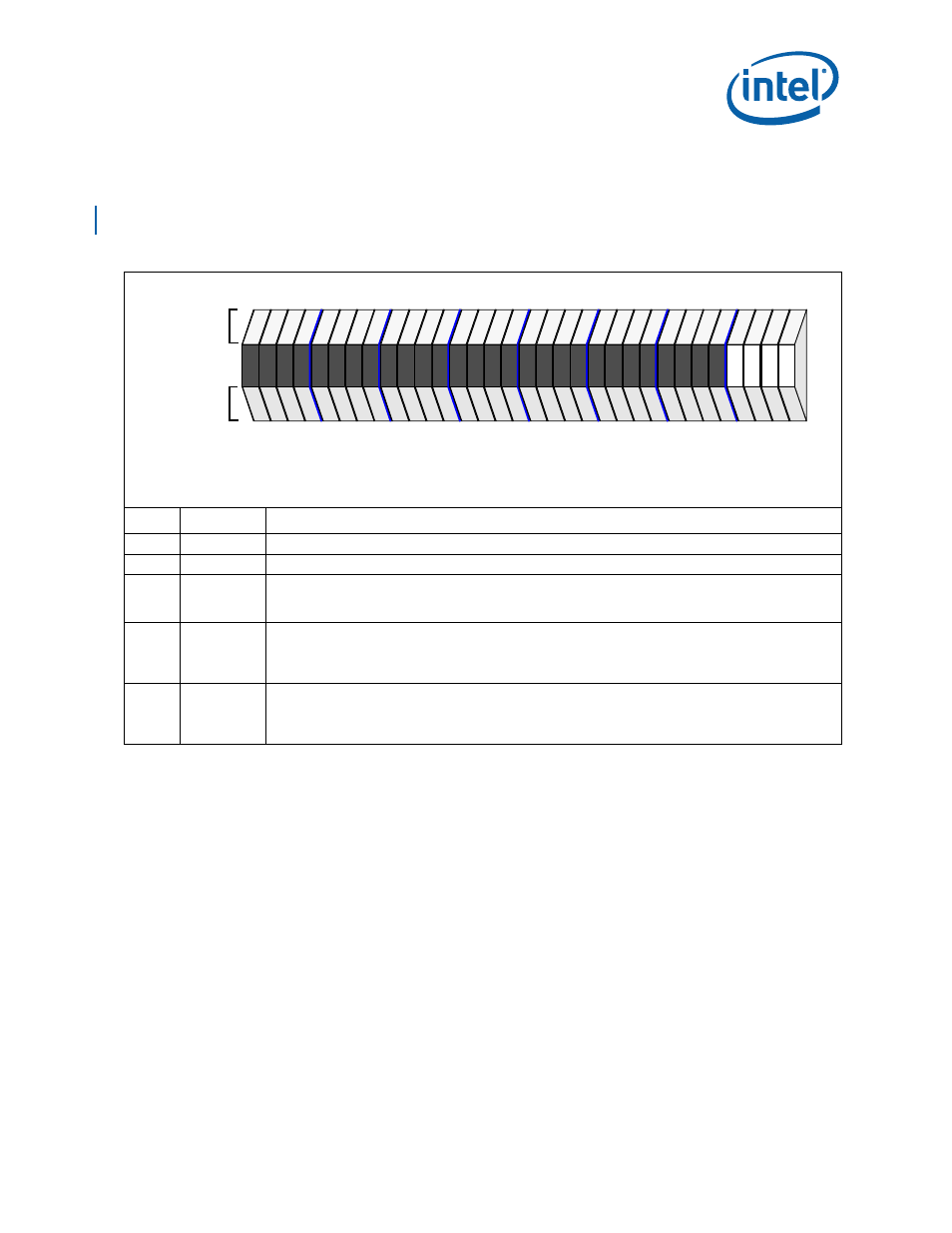

Table 352. SRAM ECC Control Register — SECR

Bit

Default

Description

31:04

000 0000H Reserved

03

1

2

Read-only as 1

2

.

02

0

2

Single Bit Error Correction Enable:

Enables or disables the correction of a single bit error.

0 = Disable single bit error correction

1 = Enable single bit error correction

01

0

2

Multi-Bit Error Reporting Enable:

Enables or disables the reporting (interrupt generation) of a

multi-bit error condition.

0 = Disable multi-bit error reporting

1 = Enable multi-bit error reporting

00

0

2

Single Bit Error Reporting Enable:

Enables or disables the reporting (interrupt generation) of a single

bit error condition.

0 = Disable single bit error reporting

1 = Enable single bit error reporting

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

ro

na

rw

na

rw

na

rw

na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Intel XScale

®

processor Local Bus Address Offset

+1508H