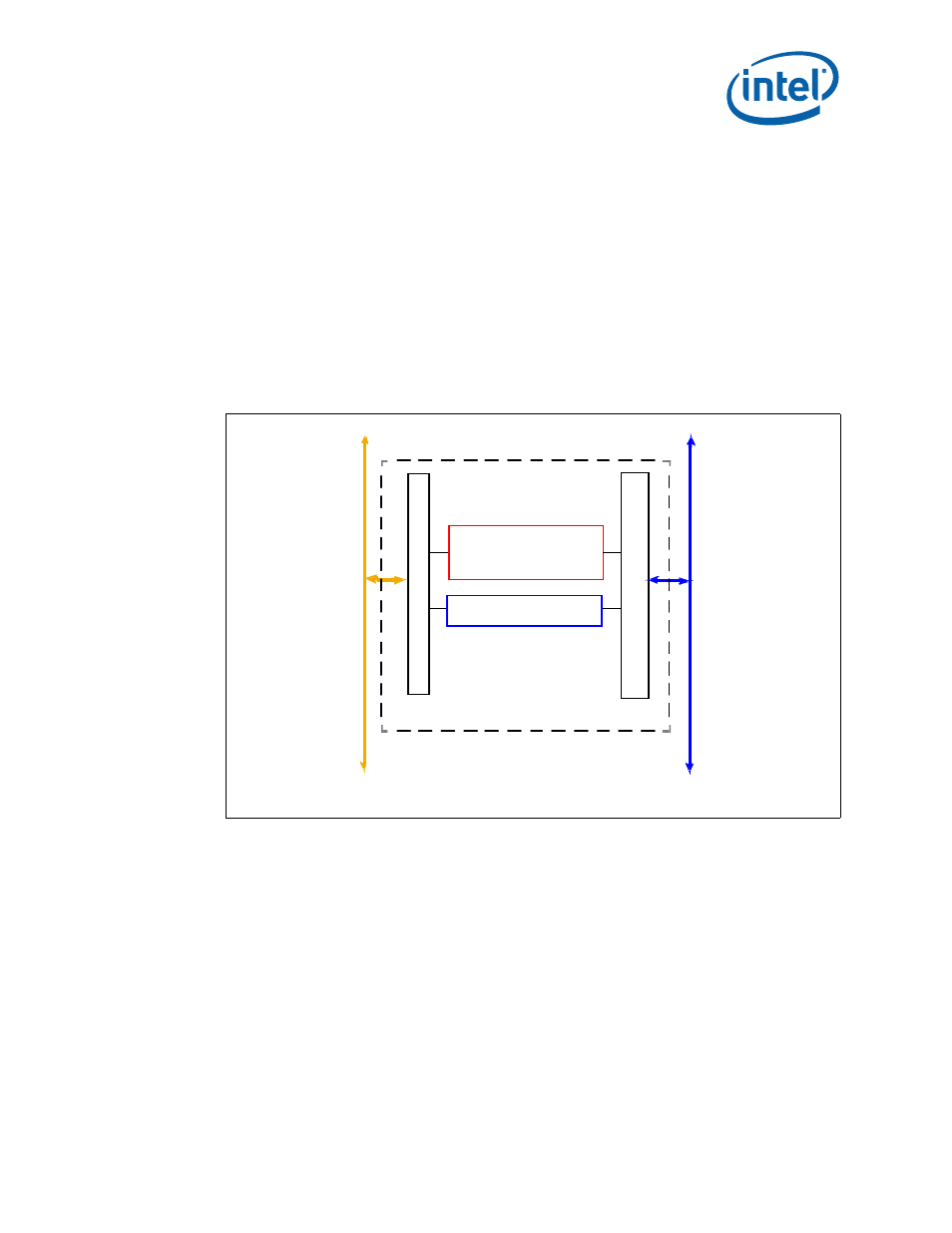

Figure 3. atu block diagram, 3 atu block diagram, Address translation unit (pci-x)—intel – Intel CONTROLLERS 413808 User Manual

Page 51

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

51

Address Translation Unit (PCI-X)—Intel

®

413808 and 413812

The 4138xx meets the standard requirements to be considered “Hot-Swap Silicon”

detailed in the Compact PCI Hot-Swap Specification, Revision 2.1.

Address and data are protected by byte-wise parity on the internal bus.

The ATU includes four extended capability headers that implement Power Management

capability as defined by the PCI Bus Power Management Interface Specification,

Revision 1.1, MSI capability as defined by PCI Local Bus Specification, Revision 2.3,

Hot-Swap capability as defined by the Compact PCI Hot-Swap Specification,

Revision 2.1, and PCI-X capability as defined by PCI-X Protocol Addendum to the PCI

Local Bus Specification, Revision 2.0.

The functionality of the ATU is described in the following sections. The ATU has a

memory-mapped register interface that is visible from either the PCI interface, the

internal bus interface, or both.

Figure 3.

ATU Block Diagram

P

C

I

B

us

Address

Translation Unit

ADDRESS TRANSLATION UNIT

Expansion ROM

Translation Unit

In

te

l®

I

/O

P

ro

ce

ss

or

In

te

rn

al

B

us

In

te

rn

al

B

us

I

nt

er

fa

ce

PC

I

B

us

I

nt

er

fa

ce

B6317-01