0 clocking and reset, 1 clocking overview, 119 intel – Intel CONTROLLERS 413808 User Manual

Page 763: Figure 119. intel

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

763

Clocking and Reset—Intel

®

413808 and 413812

17.0

Clocking and Reset

This chapter describes the clocking and reset function of the Intel

®

413808 and

413812 I/O Controllers in TPER Mode (4138xx).

17.1

Clocking Overview

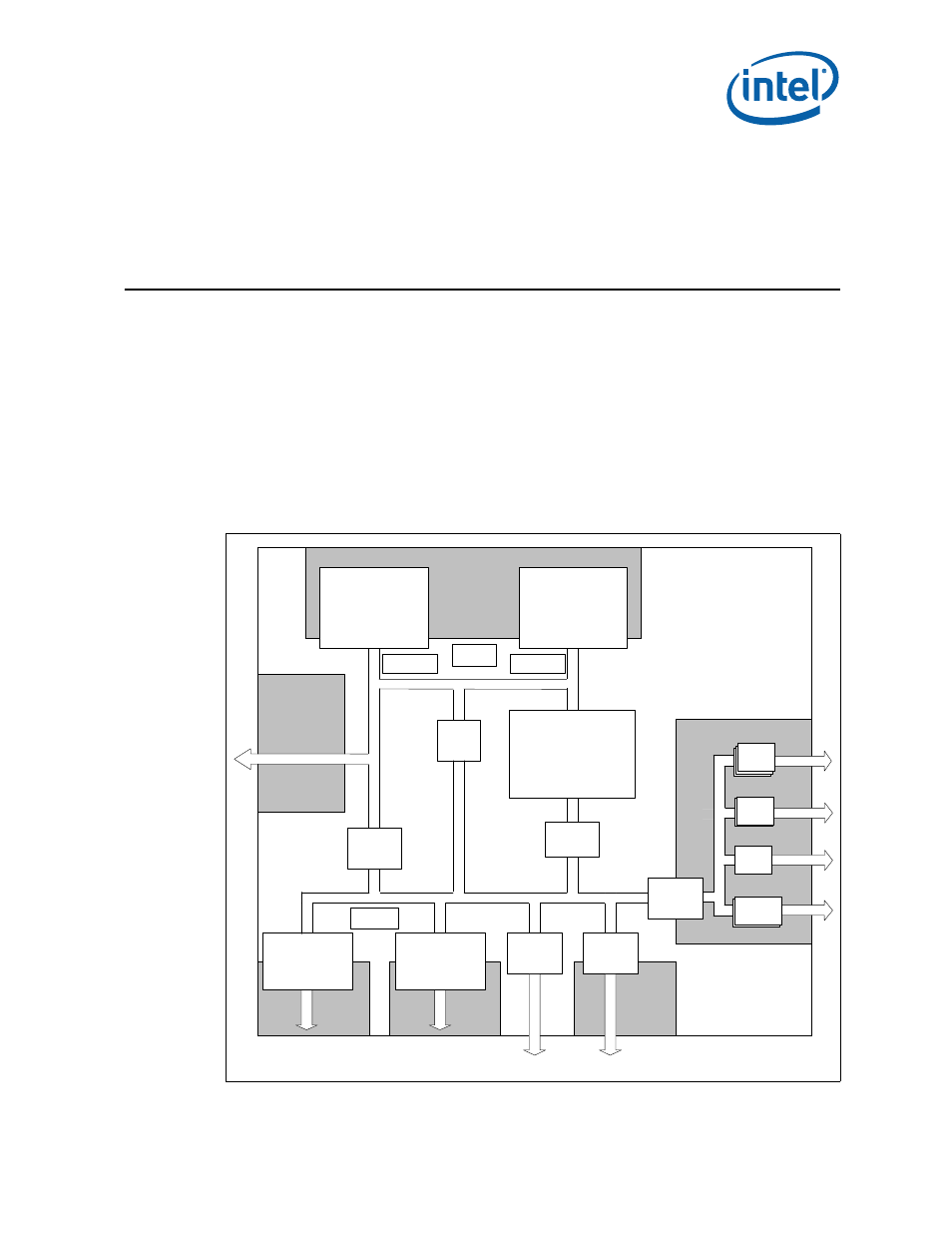

The 4138xxcontains various internal clocking boundaries. PLLs are used to generate

the clocks. One PLL for the PCI Express interface, one for PCI-X interface, one for

Memory Interface and one for everything else. Clock regions 3, 4, and 6 are driven off

the core PLL and are pseudo-synchronous to each other. There are asynchronous

boundaries between regions 1/3, regions 2/3, 6/3, and between regions 7/3.

Figure 119. Intel

®

413808 and 413812 I/O Controllers in TPER Mode Clocking Regions

Diagram

Internal

Bus

Bridge

APB

Bridge

SMBus

Peripheral

Bus

Interface

Clock Region 3

Clock Region 5

Clock Region 7

Clock

Region 8

IMU

Clock

Region 1

PCI Express

Interface

(ATUE)

PCI-X Interface

(ATUX)

Clock

Region 2

PMON

MU

Interrupt

Controller

Intel Xscale®

michroarchitecture

512K L2 Cache

512K L2 Cache

Clock

Region 4

Interrupt

Controller

UART

x2

GPIO

SGPIO

x2

Intel Xscale®

michroarchitecture

2I C x3

B6625-01

1 TDMA

and

1 SDMA

Multi-Port

SRAM Controller