Table 471. i, C control register x — icrx (sheet 2 of 2), Intel – Intel CONTROLLERS 413808 User Manual

Page 716: C bus interface units, Master abort, Transfer byte, Ack/nack control, Stop, Start, Bit default description

Intel

®

413808 and 413812—I

2

C Bus Interface Units

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

716

Order Number: 317805-001US

04

0

2

Master Abort

: used by the I

2

C unit when in master mode to generate a STOP without transmitting

another data byte.

0 = The I

2

C unit transmits STOP using the STOP ICR bit only.

1 = The I

2

C unit sends STOP without data transmission.

When in Master transmit mode, after transmitting a data byte, the ICR’s Transfer Byte bit is clear and

IDBR Transmit Empty bit is set. When no more data bytes need to be sent, setting master abort bit

sends the STOP. The Transfer Byte bit (03) must remain clear.

In master-receive mode, when a Nack is sent without a STOP (STOP ICR bit was not set) and the

4138xx

does not send a repeated START, setting this bit sends the STOP. Once again, the Transfer Byte

bit (03) must remain clear.

03

0

2

Transfer Byte

: used to send/receive a byte on the I

2

C bus.

0 = Cleared by I

2

C unit when the byte is sent/received.

1 = Send/receive a byte.

The 4138xx

can monitor this bit to determine when the byte transfer has completed. In master or slave

mode, after each byte transfer including Ack/Nack bit, the I

2

C unit holds the

SCL

line low (inserting wait

states) until the Transfer Byte bit is set.

02

0

2

Ack/Nack Control

: defines the type of Ack pulse sent by the I

2

C unit when in master receive mode.

0 = The I

2

C unit sends an Ack pulse after receiving a data byte.

1 = The I

2

C unit sends a negative Ack (Nack) after receiving a data byte.

The I

2

C unit automatically sends an Ack pulse when responding to its slave address or when responding

in slave-receive mode, independent of the Ack/Nack control bit setting.

01

0

2

STOP

: used to initiate a STOP condition after transferring the next data byte on the I

2

C bus when in

master mode. In master-receive mode, the Ack/Nack control bit must be set in conjunction with this bit.

See

Section 14.2.3.3, “STOP Condition” on page 696

for more details on the STOP state.

0 = Do not send a STOP.

1 = Send a STOP.

00

0

2

START

: used to initiate a START condition to the I

2

C unit when in master mode. See

for more details on the START state.

0 = Do not send a START.

1 = Send a START.

Table 471. I

2

C Control Register x — ICRx (Sheet 2 of 2)

Bit

Default

Description

PCI

IOP

Attributes

Attributes

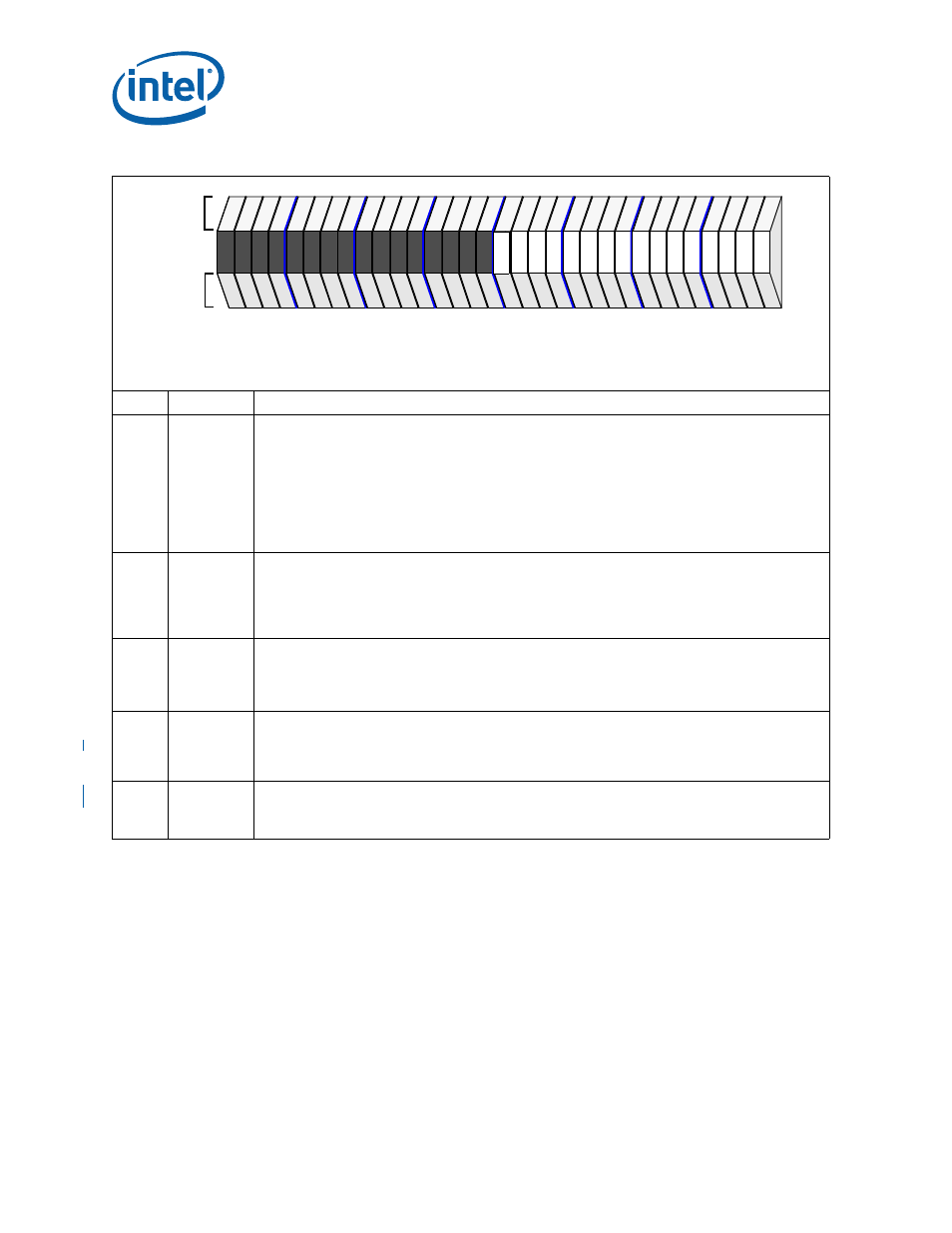

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

Unit #

0

1

2

Intel XScale

®

processor internal bus address

offset

+2500H

+2520H

+2540H

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible