3 irq interrupt vector register - iintvec, Table 385. irq interrupt vector register- iintvec, 3 irq interrupt vector register — iintvec – Intel CONTROLLERS 413808 User Manual

Page 585: 385 irq interrupt vector register- iintvec

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

585

Interrupt Controller Unit—Intel

®

413808 and 413812

10.7.3

IRQ Interrupt Vector Register — IINTVEC

The IRQ Interrupt Vector Register is a 32-bit Coprocessor 6 control register. Following

an IRQ exception, the IRQ interrupt service routine reads the 32-bit vector to the ISR

for the active IRQ source with the highest priority.

The actual vector value is a function of the INTBASE and the INTSIZE registers and is

based on a fixed order of all 128 possible interrupt sources. The vectors begin at

INTBASE with source 0 (i.e., IINTSRC0 bit 0), and end at INTBASE + INTSIZE (per

source)*127 with source 127 (that is, IINTSRC3 bit 31).

Before returning to User Mode from Interrupt Mode, the software reads the IINTVEC

register and process any lower priority IRQ sources that are active. When there are no

longer any active IRQ sources, a read from the IINTVEC register returns FFFF FFFFH.

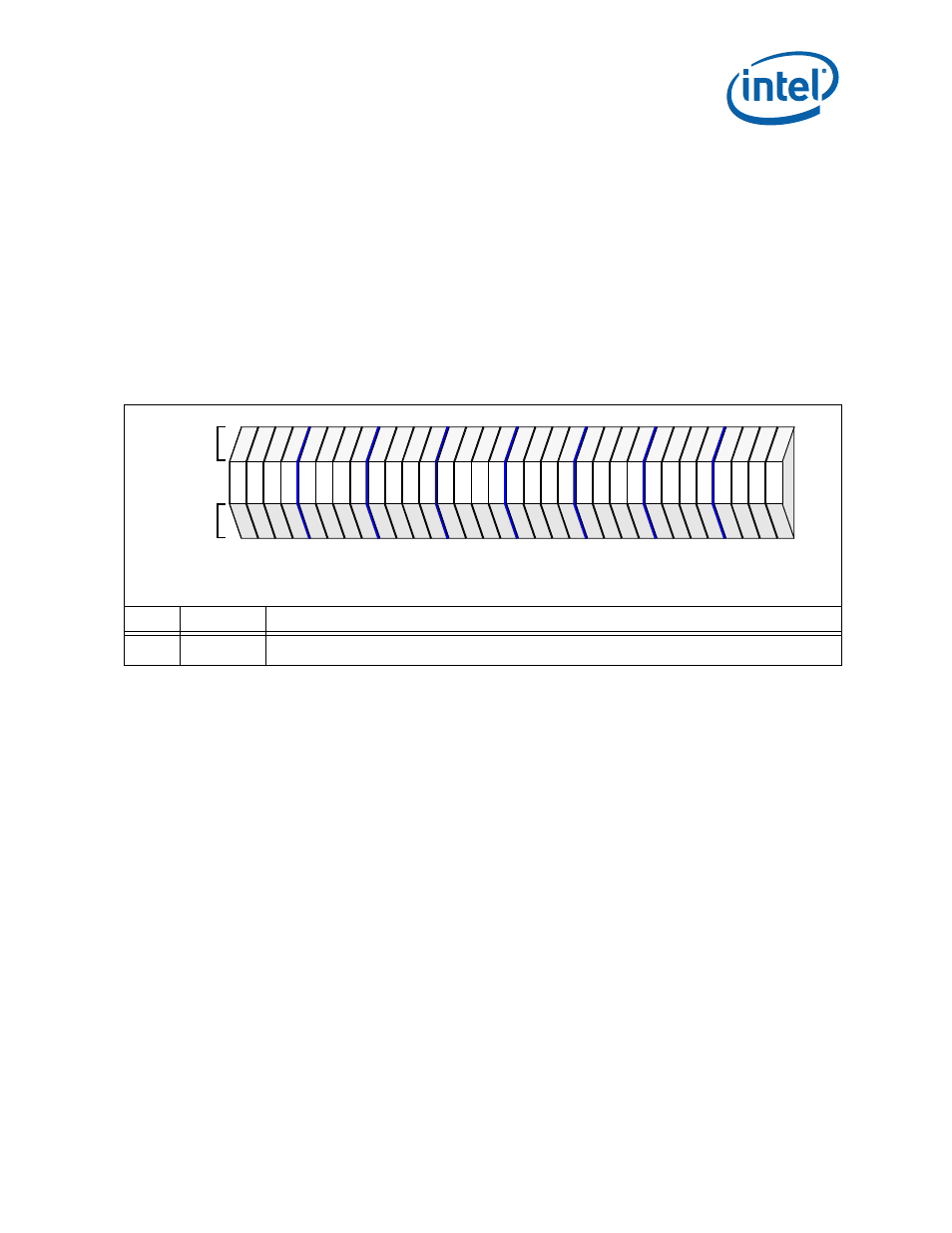

Table 385. IRQ Interrupt Vector Register- IINTVEC

Bit

Default

Description

31:00

00000000H IRQ Interrupt Vector—Vector to the highest priority active IRQ source. This register reads FFFF FFFFH

when there are no active IRQ sources.

Memory

Coprocessor

Attributes

Attributes

28

24

20

16

12

8

4

0

31

ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro

na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Intel XScale

®

processor Coprocessor address

CP6, Page 2, Register 3