Table 265. message unit registers, 265 message unit registers – Intel CONTROLLERS 413808 User Manual

Page 411

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

411

Messaging Unit—Intel

®

413808 and 413812

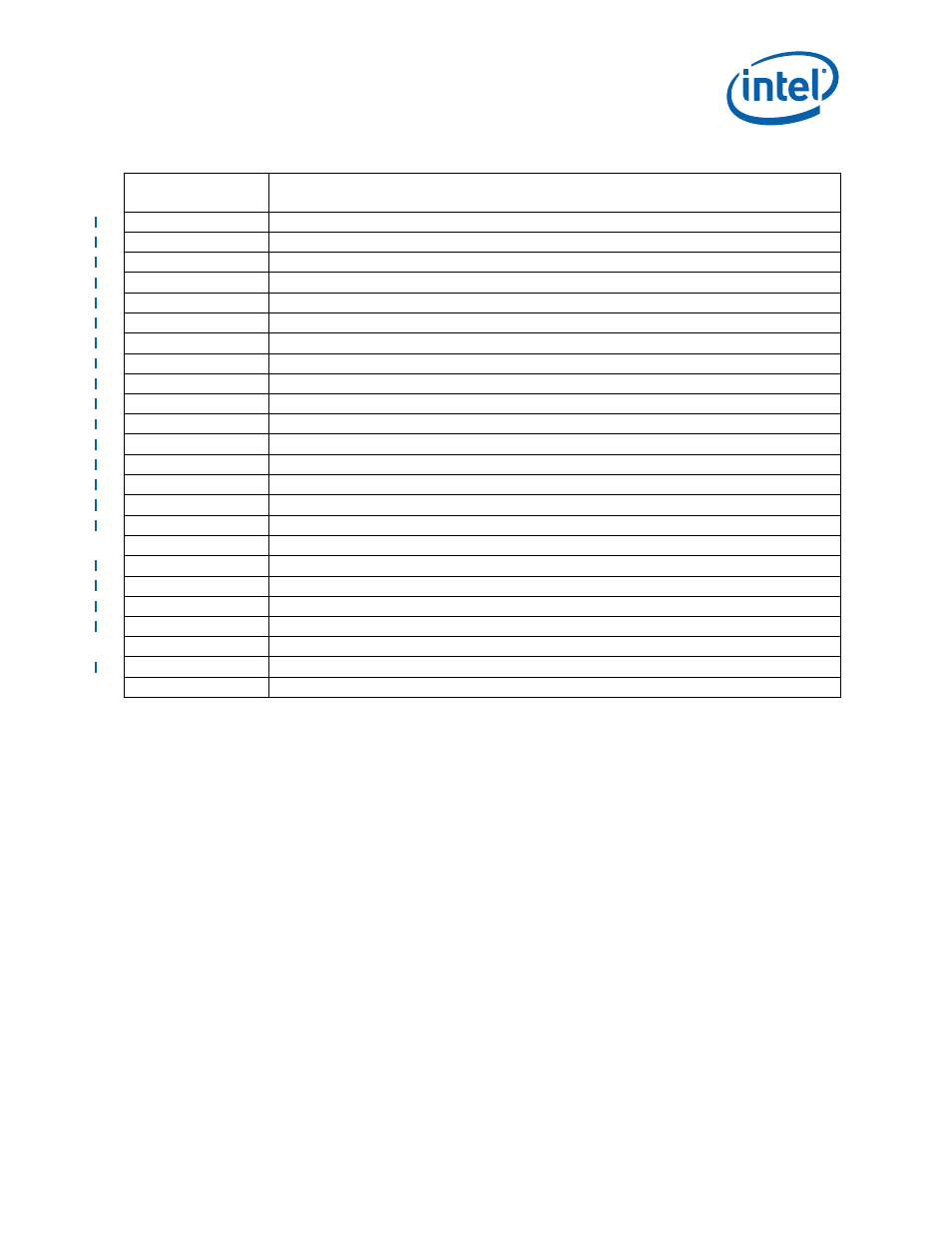

Table 265. Message Unit Registers

Internal Bus Address

Offset

Section, Register Name - Acronym (Page)

4010H

Section 4.7.1, “Inbound Message Register - IMRx” on page 412

4014H

Section 4.7.1, “Inbound Message Register - IMRx” on page 412

4018H

Section 4.7.2, “Outbound Message Register - OMRx” on page 412

401CH

Section 4.7.2, “Outbound Message Register - OMRx” on page 412

4020H

Section 4.7.3, “Inbound Doorbell Register - IDR” on page 413

4024H

Section 4.7.4, “Inbound Interrupt Status Register - IISR” on page 414

4028H

Section 4.7.5, “Inbound Interrupt Mask Register - IIMR” on page 415

402CH

Section 4.7.6, “Outbound Doorbell Register - ODR” on page 416

4030H

Section 4.7.7, “Outbound Interrupt Status Register - OISR” on page 417

4034H

Section 4.7.8, “Outbound Interrupt Mask Register - OIMR” on page 418

4038H

Section 4.7.9, “Inbound Reset Control and Status Register - IRCSR” on page 419

403CH

Section 4.7.10, “Outbound Reset Control and Status Register - ORCSR” on page 420

4048H

Section 4.7.11, “MSI Inbound Message Register — MIMR” on page 421

4050H

Section 4.7.12, “MU Configuration Register - MUCR” on page 422

4084H

Section 4.7.13, “MU Base Address Register - MUBAR” on page 423

4088H

Section 4.7.14, “MU Upper Base Address Register - MUUBAR” on page 424

408CH - 4FFCH

Reserved,

50

X

0H

Section 4.7.15, “MU MSI-X Table Message Address Registers - M_MT_MAR[0:7]” on page 425

50

X

4H

Section 4.7.16, “MU MSI-X Table Message Upper Address Registers - M_MT_MUAR[0:7]” on page 426

50

X

8H

Section 4.7.17, “MU MSI-X Table Message Data Registers - M_MT_MDR[0:7]” on page 427

50

X

Section 4.7.18, “MU MSI-X Table Message Vector Control Registers - M_MT_MVCR[0:7]” on page 428

5080H - 57FCH

Reserved.

5800H

Section 4.7.19, “MU MSI-X Pending Bits Array Register - M_MPBAR” on page 429

5804H - 5FFCH

Reserved.

Notes:

1.

X is equal to 0H, 1H, 2H, 3H, 4H, 5H, 6H, or 7H.

2.

X is equal to 0H, 1H, 2H, 3H, 4H, 5H, 6H, or 7H.

3.

X is equal to 0H, 1H, 2H, 3H, 4H, 5H, 6H, or 7H.

4.

X is equal to 0H, 1H, 2H, 3H, 4H, 5H, 6H, or 7H.