Table 28. pci-x pad registers, 28 pci-x pad registers, Table 27 – Intel CONTROLLERS 413808 User Manual

Page 146

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

146

Order Number: 317805-001US

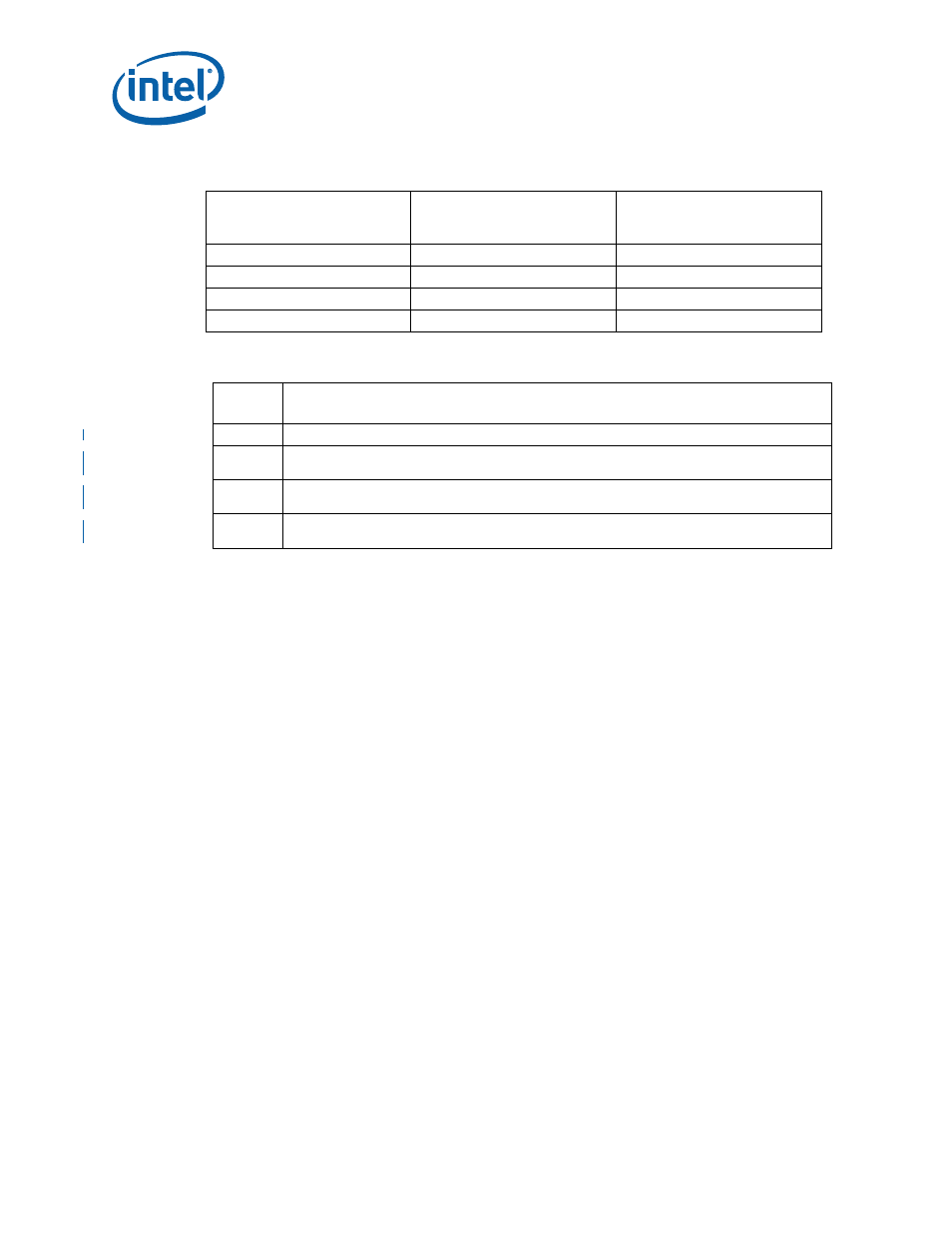

Table 27. ATU Internal Bus Memory Mapped Register Range Offsets

INTERFACE_SEL_PCIX#

CONTROLLER_ONLY#

Internal Bus MMR Address

Range Offset

(Relative to PMMRBAR)

Asserted (0)

Deasserted (1)

+4 8000H

Asserted (0)

Asserted (0)

+4 C000H

Deasserted (1)

Asserted (0)

+4 C000H

Deasserted (1)

Deasserted (1)

+4 D000H

Table 28. PCI-X Pad Registers

Register

Offset

Section, Register Name - Acronym (Page)

2100H

Section 2.14.88, “PCIX RCOMP Control Register — PRCR” on page 226

2104H

Section 2.14.89, “PCIX Pad ODT Drive Strength Manual Override Values Registers —

2108H

Section 2.14.90, “PCIX PAD DRIVE STRENGTH Manual Override Values Register (3.3 V/1.5 V

Switch Supply Voltage) — PPDSMOVR3.3_1.5” on page 228

210CH

Section 2.14.91, “PCIX PAD DRIVE STRENGTH Manual Override Values Register (3.3 V Dedicated