6 peripheral memory-mapped register address space, 523 local addresses for integrated peripherals – Intel CONTROLLERS 413808 User Manual

Page 798

Intel

®

413808 and 413812—Peripheral Registers

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

798

Order Number: 317805-001US

19.6

Peripheral Memory-Mapped Register Address Space

The PMMR address space is divided to support the integrated peripherals on the

4138xx.

shows all of the 4138xx integrated peripheral memory-mapped

registers and their internal bus address offsets. The starting address of the

memory-mapped registers is programmable using the PMMRBAR register. The

PMMRBAR register is located at a fixed location which is at F_FFFF_FFFCH. The default

starting address of the PMMR register block is at 0_FFD8_0000H.

lists the peripherals and the relative address offsets from the PMMRBAR

content.

Warning:

Care must be exercised when updating memory-mapped registers, because some of

the registers can have side-effects on other registers and resources in the 4138xx

architecture. As an example, updating a Base Address Register (such as the PMMRBAR)

relocates other registers and resources in the 4138xx architecture, and software must

not access these related registers and resources until software can ensure that the

Base Address Register has truly been updated. Refer to the Intel XScale

®

Microarchitecture Developer’s Manual, which describes various methods of fencing

memory accesses.

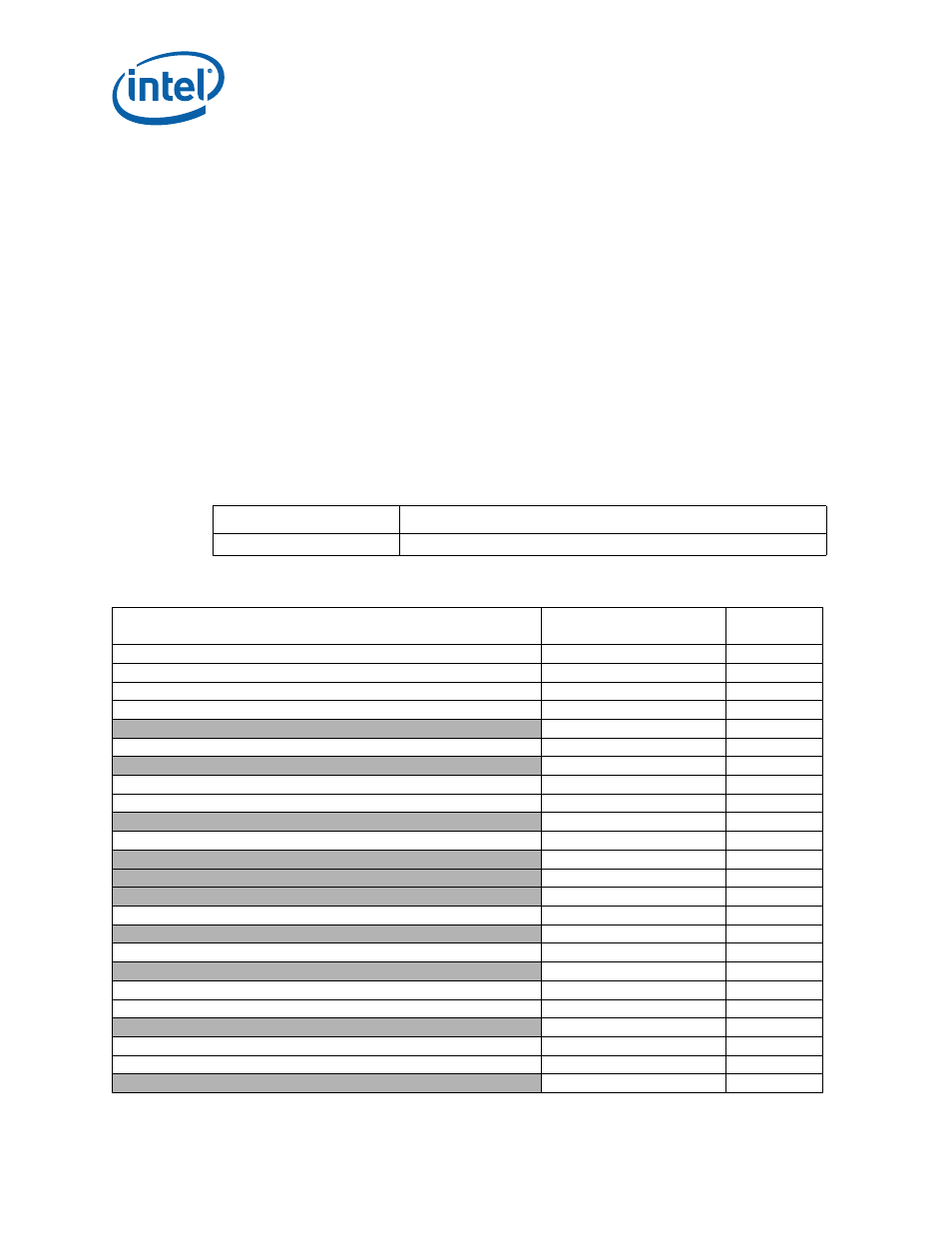

Table 522. PMMR Base Address Register (PMMRBAR) Default Value

Register

Absolute Address

PMMRBAR

F_FFFF_FFFCH

Table 523. Local Addresses for Integrated Peripherals (Sheet 1 of 3)

Integrated Peripheral

Internal Address Offset

(Relative to PMMRBAR)

Space

Allocated

Reserved.

+0000H through 01FFH

512 Bytes

Reserved.

+0200H through 03FFH

512 Bytes

Reserved.

+0400H through 05FFH

512 Bytes

Reserved.

+0600H through 07FFH

512 Bytes

Not Claimed by any Unit

a

+0800H through 09FFH

x

Reserved.

+0A00H through 0CFFH

768 Bytes

Not Claimed by any Unit

+0D00H through 14FFH

x

Reserved.

+1500H through 157FH

128 Bytes

“Peripheral Bus Interface Unit”

+1580H through 15FFH

128 Bytes

Not Claimed by any Unit

+1600H through 163FH

x

+1640H through 164FH

16 Bytes

Not Claimed by any Unit

+1650H through 167FH

32 Bytes

Not Claimed by any Unit

+1680H through 16FFH

x

Not Claimed by any Unit

+1700H through 177FH

x

+1780H through 1797H

24 Bytes

Not Claimed by any Unit

+1798H through 177FH

104 Bytes

Reserved.

+1800H through 19FFH

512 Bytes

Not Claimed by any Unit

+1A00H through 1FFFH

x

+2000H through 21FFH

512 Bytes

Reserved

+2200H through 221FH

32 Bytes

Not Claimed by any Unit

+2220H through 22FFH

x

+2300H through 233FH

64 Bytes

+2340H through 237FH

64 Bytes

Not Claimed by any Unit

+2380H through 247FH

x