1 sgpio interface control register x - sgicrx, 1 sgpio interface control register x — sgicrx, 321 sgpio interface control register x - sgicrx – Intel CONTROLLERS 413808 User Manual

Page 475: Table 321, “sgpio interface control, Sgpio unit—intel, Bit default description, Intel, Sgpio # 0 1 intel xscale

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

475

SGPIO Unit—Intel

®

413808 and 413812

6.6.1

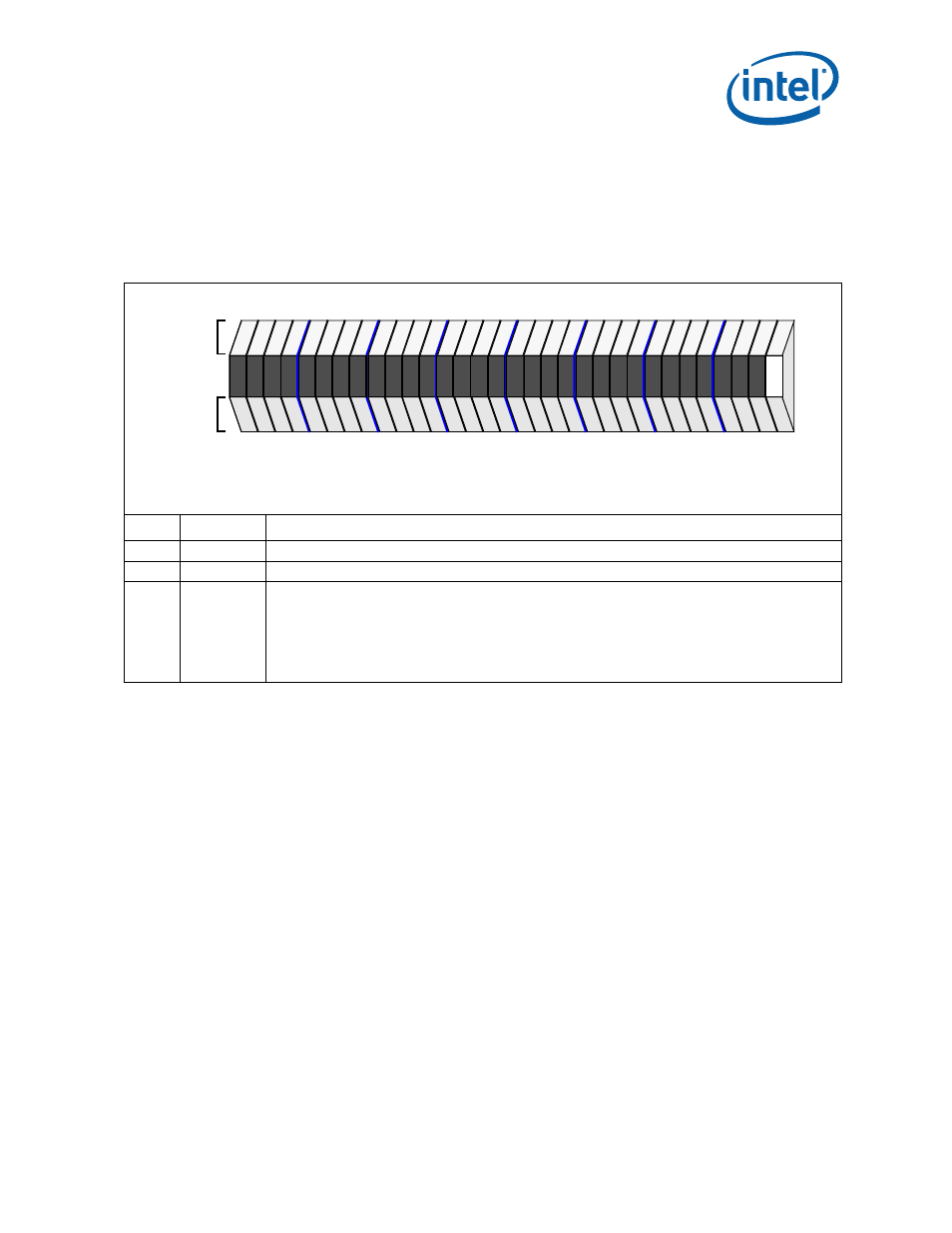

SGPIO Interface Control Register x — SGICRx

The SGPIO Interface Control Register x - SGPICRx is used to select the SGPIO unit

mode of operations - SGPIO bus or direct LED interface. Each SGPIO unit can either

drive eight output signals on the serial SGPIO bus or directly drive the eight output

signals on eight separate pins.

Table 321. SGPIO Interface Control Register x - SGICRx

Bit

Default

Description

31:16

0000H

Reserved.

15:01

0000H

Reserved.

00

0

2

SGPIO x Functionality Enable:

For SGPIO unit 0 - When this bit is set, the SGPIO bus pins (S_ACT[0], S_STAT[0], S_ACT[2] and

S_STAT[2]) are used for SGPIO signaling. When cleared, the SGPIO pins are used for direct LED

controls.

For SGPIO unit 1 - When this bit is set, the SGPIO bus pins (S_ACT[4], S_STAT[4], S_ACT[6], and

S_STAT[6]) are used for SGPIO signaling. When cleared, the SGPIO pins are used for direct LED

controls.

Coprocessor

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rw

na

SGPIO #

0

1

Intel XScale

®

processor internal bus address offset

+2600H

+2680H

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible