Intel CONTROLLERS 413808 User Manual

Page 307

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

307

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

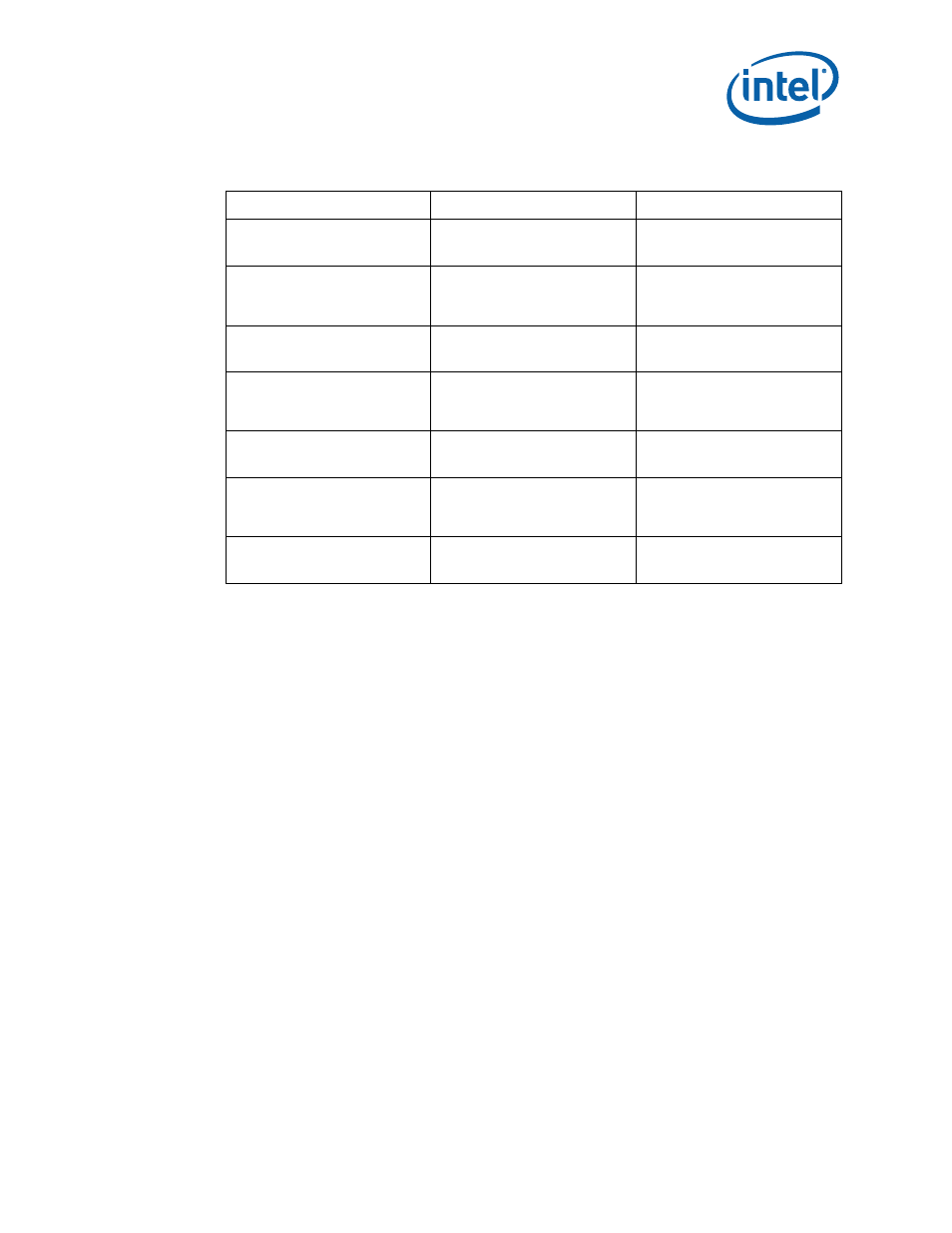

Table 155. ATU Base Registers and Associated Limit Registers

Base Address Register

Limit Register

Description

Inbound ATU Base Address

Register 0

Inbound ATU Limit Register 0

Defines the inbound translation

window 0 from the PCI Express

Link.

Inbound ATU Upper Base Address

Register 0

N/A

Together with ATU Base Address

Register 0 defines the inbound

translation window 0 from the PCI

Express Link

Inbound ATU Base Address

Register 1

Inbound ATU Limit Register 1

Defines the inbound translation

window 1 from the PCI Express

Link.

Inbound ATU Upper Base Address

Register 1

N/A

Together with ATU Base Address

Register 1 defines the inbound

translation window 1 from the PCI

Express Link

Inbound ATU Base Address

Register 2

Inbound ATU Limit Register 2

Defines the inbound translation

window 2 from the PCI Express

Link.

Inbound ATU Upper Base Address

Register 2

N/A

Together with ATU Base Address

Register 2 defines the inbound

translation window 2 from the PCI

Express Link

Expansion ROM Base Address

Register

Expansion ROM Limit Register

Defines the window of addresses

used by a bus master for reading

from an Expansion ROM.