19 mu msi-x pending bits array register - m_mpbar, 20 msi capability identifier register - cap_id, 284 mu msi-x pending bits array register - m_mpbar – Intel CONTROLLERS 413808 User Manual

Page 429: Section 4.7.20, “msi, Capability identifier register - cap_id

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

429

Messaging Unit—Intel

®

413808 and 413812

4.7.19

MU MSI-X Pending Bits Array Register - M_MPBAR

The MU MSI-X Pending Bits Array Register contains the contains the pending bits for

the eight MU interrupt sources. When an entry in the MSI-X table is masked in the

Vector Control Register, the software may service that interrupt request by polling the

pending bit.

Note:

The M_MPBAR register is not reset with an internal bus reset.

4.7.20

MSI Capability Identifier Register - Cap_ID

The MSI Capability Identifier Register bits adhere to the definitions in the PCI Local Bus

Specification, Revision 2.2. This register in the PCI Interface Extended Capability

header identifies the type of Extended Capability contained in that header. The value of

05H in this field identifies the function as message signaled interrupt capable.

Note:

Refer to the Peripheral Registers Chapter for the default internal bus address. This

register is part of the configuration space of the Address Translation Unit that is setup

as an endpoint.

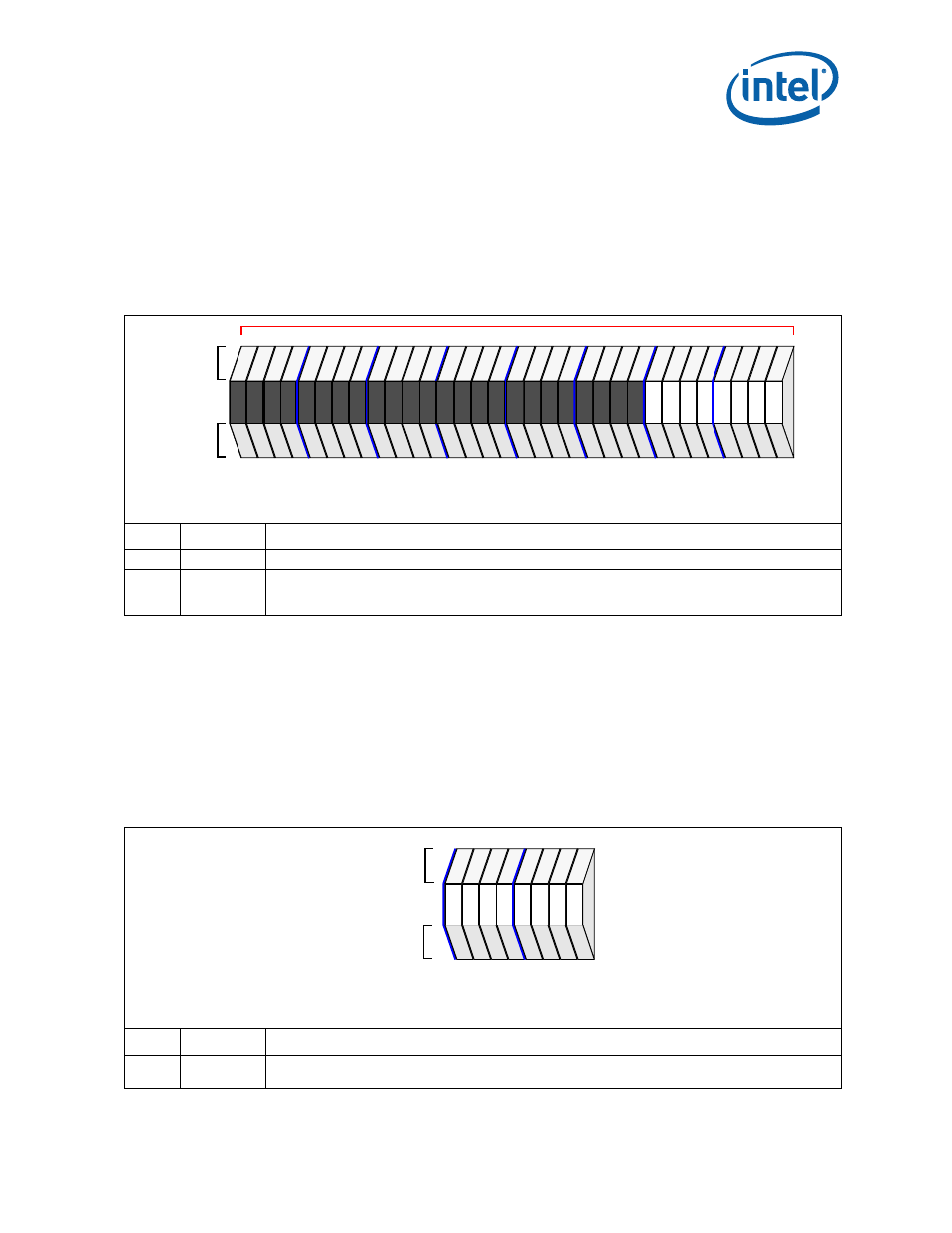

Table 284. MU MSI-X Pending Bits Array Register - M_MPBAR

Bit

Default

Description

31:08

0000 000H Reserved.

07:00

00000000

2

Pending Bits Array: Any bit that is set indicates that the associated MSI-X message is scheduled to be

sent. When an associated entry in the MSI-X table is masked using the mask bit in the Vector Control

Register, software can service the interrupt based on polling the associated pending bit.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv ro ro ro ro ro ro ro ro

rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv ro ro ro ro ro ro ro ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

M_MPBAR

internal bus address

offset

5800H

M_MPBAR

MU/PCI Base Address

Offset

1800H

Table 285. MSI Capability Identifier Register - MSI_Cap_ID

Bit

Default

Description

07:00

05H

MSI_Cap_Id

- This field with its 05H value identifies this item in the linked list of Extended Capability

Headers as being the message signaled interrupt capability item.

PCI

IOP

Attributes

Attributes

7

4

0

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

PCI Configuration Offset

A0H

Internal Bus Address Offset

0A0H