General purpose i/o unit—intel, Gpio[5, P_rst – Intel CONTROLLERS 413808 User Manual

Page 727: Gpio[4, Gpio[3, Gpio[2, Gpio[1, Gpio[0, Bit default description

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

727

General Purpose I/O Unit—Intel

®

413808 and 413812

05

GPIO[5]

during

P_RST#

assertion

GPIO5 Input Data — This bit reflects the state of the

GPIO[5]

pin.

04

GPIO[4]

during

P_RST#

assertion

GPIO4 Input Data — This bit reflects the state of the

GPIO[4]

pin.

03

GPIO[3]

during

P_RST#

assertion

GPIO3 Input Data — This bit reflects the state of the

GPIO[3]

pin.

02

GPIO[2]

during

P_RST#

assertion

GPIO2 Input Data — This bit reflects the state of the

GPIO[2]

pin.

01

GPIO[1]

during

P_RST#

assertion

GPIO1 Input Data — This bit reflects the state of the

GPIO[1]

pin.

00

GPIO[0]

during

P_RST#

assertion

GPIO0 Input Data — This bit reflects the state of the

GPIO[0]

pin.

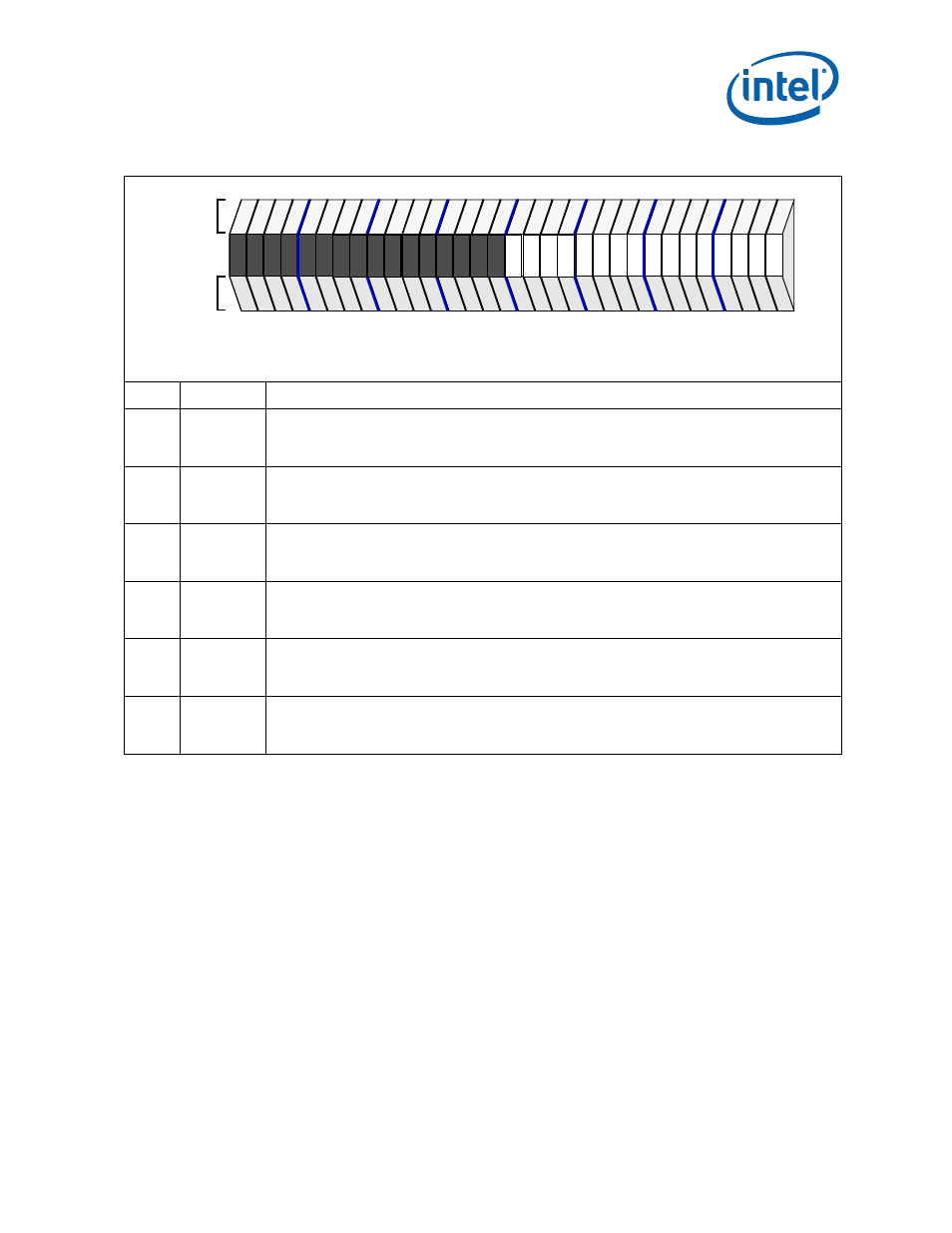

Table 479. GPIO Input Data Register — GPID (Sheet 2 of 2)

Bit

Default

Description

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Intel XScale

®

processor Local Bus Address

offset

+2484H