63 hs_cntrl - hot-swap control/status register, 63hs_cntrl - hot-swap control/status register, 90 hs_cntrl - hot-swap control/status register – Intel CONTROLLERS 413808 User Manual

Page 202

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

202

Order Number: 317805-001US

2.14.63 HS_CNTRL - Hot-Swap Control/Status Register

The 4138xx meets the standard requirements to be considered “Hot-Swap Silicon”

detailed in the Compact PCI Hot-Swap Specification, Revision 2.1. Refer to the

Compact PCI Hot-Swap Specification, Revision 2.1 for more details on the insertion and

extraction processes.

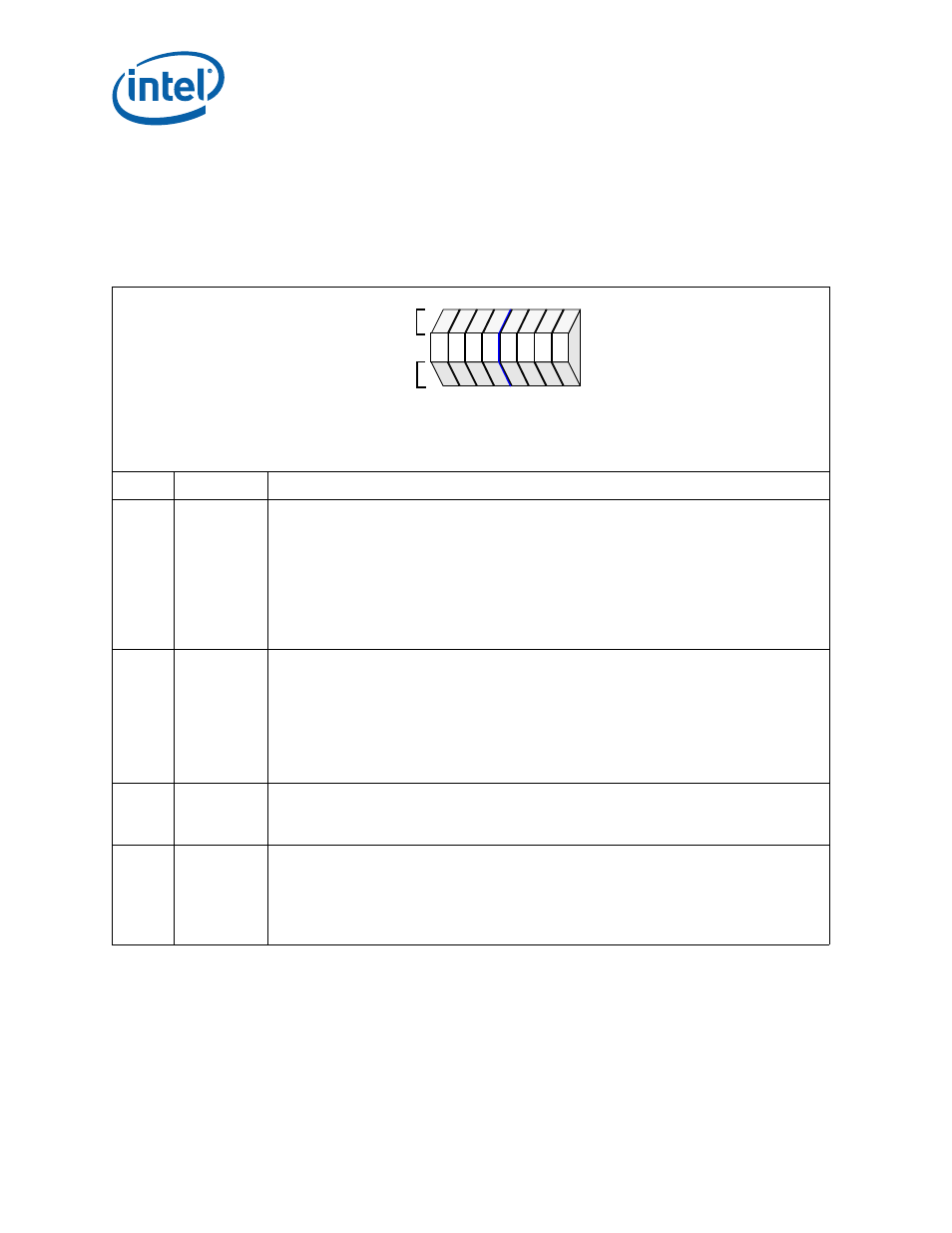

Table 90. HS_CNTRL - Hot-Swap Control/Status Register (Sheet 1 of 2)

Bit

Default

Description

07

1b

(This bit

actually

powers up to

0b, however

4138xx sets it

to 1b prior to

any host

software

access to the

device)

INS: Freshly INSerted board. 4138xx sets this bit to a 1b following the de-assertion of P_RST#

provided that L_STAT is sampled low indicating that the ejector handle closed.

The INS bit is cleared when software writes a 1b to it. Writing 0b to this bit has no effect.

1 = 4138xx asserts P_ENUM#, (when not masked by bit(1) of this register), to indicate that the

card is freshly inserted and is ready to be configured by system software.

After system software has cleared this bit (by writing a 1b to it) 4138xx de-asserts P_ENUM# (when

currently asserted), and is then armed for a possible future extraction event (EXT bit assertion is

enabled).

06

0b

EXT:

Pending EXTraction of board. 4138xx sets this bit to a 1b when:

• (LOO = 0b or DHA = 0b), and

• L_STAT is sampled high while P_RST# is deasserted indicating that the ejector handle is

unlocked, and

• The board is currently in the INSERTED state (i.e., the INS bit = 0b).

The EXT bit is cleared when software writes a 1b. Writing a 0b has no effect. When 1b: 4138xx

asserts P_ENUM#, (when not masked by bit(1) of this register), to indicate that the card is about to

be removed.

05:04

01b

PI:

Programming Interface

This field is hard-wired to 01b indicating that 4138xx supports Device Hiding and PIE bit

functionality.

03

0b

LOO:

LED On/Off (LOO) Control. Allows software control of the LED.

0 = 4138xx drives LED_OUT low turning the external LED off.

1 = 4138xx drives LED_OUT high illuminating the external LED.

Note:

Additional external LED control logic must be ORed with 4138xx LED_OUT signal to ensure

that the blue LED is illuminated while P_RST# is asserted or when the board is in the H0,

H1, or H1F cPCI Hot-Swap defined hardware states.

PCI

IOP

Attributes

Attributes

7

4

0

rw

rc

rw

rc

ro

ro

ro

ro

rw

rw

ro

ro

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

RW = Read/Write

RO = Read Only

RT = Read/Toggle

RC = Read/Clear

SW = SROM Write

NA = Not Accessible

Register Offset

+0EAH