11 uart x fifo occupancy register, 11uart x fifo occupancy register, 461 uart x fifo occupancy register - (uxfor) – Intel CONTROLLERS 413808 User Manual

Page 686

Intel

®

413808 and 413812—UARTs

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

686

Order Number: 317805-001US

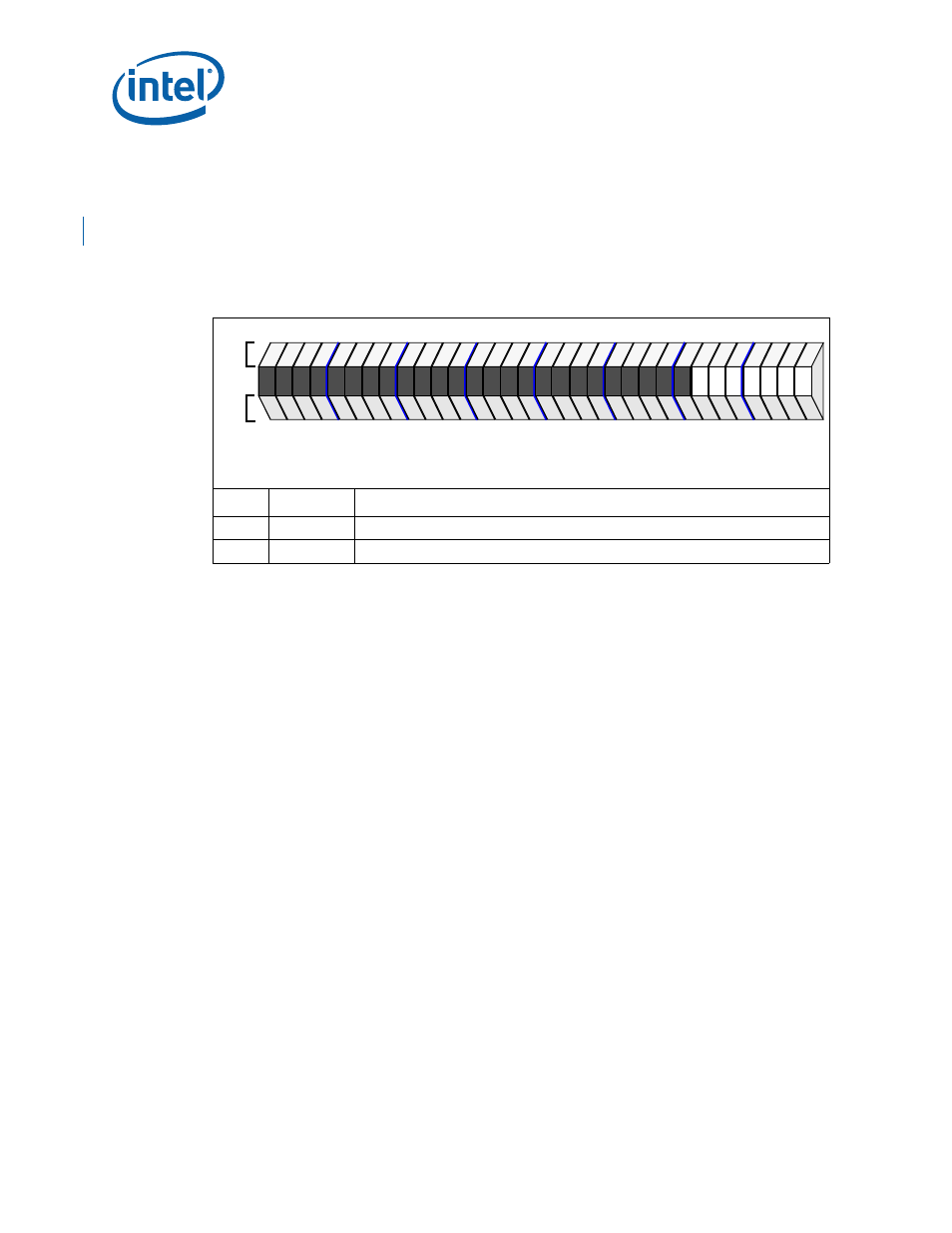

13.4.11 UART x FIFO Occupancy Register

This register shows the number of bytes currently remaining the Receive FIFO. It can

be used by the processor to determine the number of trailing bytes to remove from the

receive FIFO when the Character Time-out Interrupt is detected. Refer to

13.3.2, “Removing Trailing Bytes In Interrupt Mode” on page 664

. The FOR register is

incremented once for each byte of data written to the Receive FIFO and decremented

once for each byte read.

Table 461. UART x FIFO Occupancy Register - (UxFOR)

Bit

Default

Description

31:7

000 0000h

Reserved

6:0

000 0000

2

FOR[6:0]: Number of bytes (0-63) remaining in the Receiver FIFO

PC

I

IO

P

A

tt

ri

bu

te

s

A

tt

ri

bu

te

s

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

Unit #

01

Intel XScale

®

Core internal bus address

+2324H (DLAB=x)

+2364H (DLAB=x)

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible