14 register definitions, 1 pci configuration registers, 15 atu interface configuration header format – Intel CONTROLLERS 413808 User Manual

Page 139

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

139

Address Translation Unit (PCI-X)—Intel

®

413808 and 413812

2.14

Register Definitions

Every PCI device implements its own separate configuration address space and

configuration registers. The PCI Local Bus Specification, Revision 2.3 requires that

configuration space be 256 bytes, and the first 64 bytes must adhere to a predefined

header format.

defines the header format.

shows the PCI configuration registers,

listed by internal bus address offset.

shows the entire ATU configuration space

(including header and extended registers) and the corresponding section that describes

each register. Note that all configuration read and write transactions is accepted on the

internal bus as 32-bit transactions. Refer to

Chapter 19.0, “Peripheral Registers”

.

2.14.1

PCI Configuration Registers

The ATU is programmed via a Type 0 configuration command on the PCI interface. See

Section 2.2.1.4, “Inbound Configuration Cycle Translation” on page 64

. ATU

configuration space is function number zero of the 4138xx single-function PCI device.

Beyond the required 64 byte header format, ATU configuration space implements

extended register space in support of the units functionality. Refer to the PCI Local Bus

Specification, Revision 2.3 for details on accessing and programming configuration

register space.

The ATU unit includes six extended capability configuration spaces beginning at

configuration offsets 90H, 98H, A0H, B0H, D0H, and E8H. The extended configuration

spaces can be accessed by a device on the PCI interface through a mechanism defined

in the PCI Local Bus Specification, Revision 2.3.

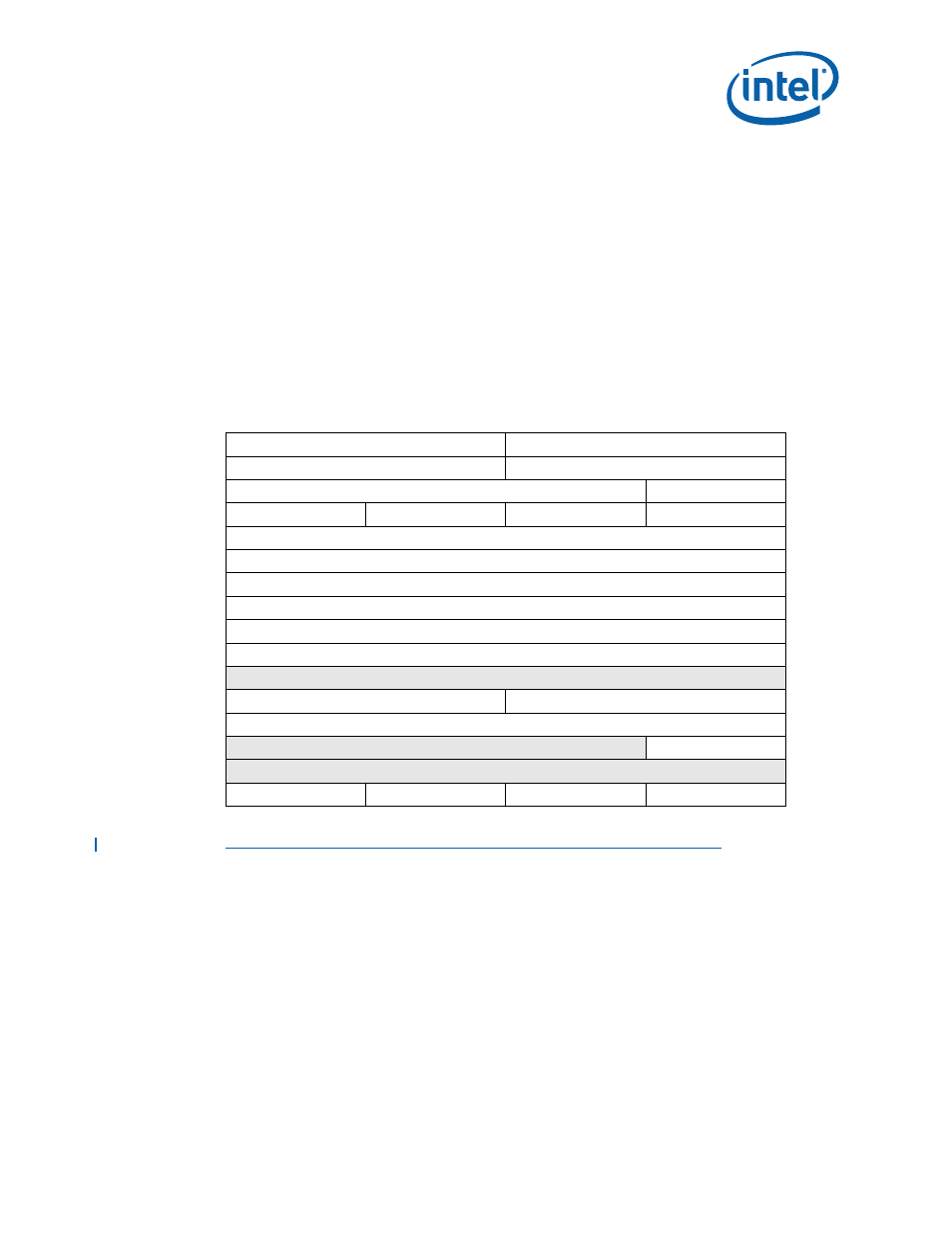

Figure 15. ATU Interface Configuration Header Format

ATU Device ID

Vendor ID

00H

Status

Command

04H

ATU Class Code

Revision ID

08H

ATUBISTR

Header Type

Latency Timer

Cacheline Size

0CH

Inbound ATU Base Address 0

10H

Inbound ATU Upper Base Address 0

14H

Inbound ATU Base Address 1

18H

Inbound ATU Upper Base Address 1

1CH

Inbound ATU Base Address 2

20H

Inbound ATU Upper Base Address 2

24H

Reserved

28H

ATU Subsystem ID

ATU Subsystem Vendor ID

2CH

Expansion ROM Base Address

30H

Reserved

Capabilities Pointer

34H

Reserved

38H

Maximum Latency

Minimum Grant

Interrupt Pin

Interrupt Line

3CH